전력 전자 장치 소개

무접점 계전기 및 무접점 모듈의 작업은 내부 전력 전자 장치와 불가분의 관계이므로 전력 전자 장치에 대한 몇 가지 기본 지식을 소개할 필요가 있습니다. 이 기사를 통해 전력 전자 장치가 무엇인지 배울 것입니다. 그들은 어떻게 작동합니까? 그들의 기본 특성은 무엇입니까? 그것들을 사용하는 방법?

아래의 DIRECTORY 와 브라우저 오른쪽의 QUICK NAVIGATOR 를 통해 관심있는 장으로 빠르게 이동할 수 있습니다.

CONTENTS

§1.전력 전자 장치 란 무엇입니까? |

§2.제어할 수 없는 장치란 무엇입니까? |

§3.트랜지스터란? |

§4.반 제어 장치 란 무엇입니까? |

§5.완전 제어 장치 란 무엇입니까? |

§6.전력 전자 장치를 선택하는 방법 |

§7.전력전자기기 사용법 |

§1.전력 전자 장치 란 무엇입니까?

전력기기 또는 전력계통에서 주 회로는 전기에너지의 변화 또는 제어를 실현하는 데 사용되며, 전력전자소자(PED)는 주 회로의 핵심이다. 이전에 전력 전자 장치에는 전력 진공 장치(예: 수은 아크 정류기, 사이러트론) 및 전력 반도체 장치(예: 전력 다이오드, 사이리스터)가 포함되었습니다. 전력 반도체 소자는 비용과 성능 면에서 명백한 이점으로 인해 점차적으로 전력 진공 소자의 위치를 대체하고 있으며, 따라서 오늘날 소위 전력 전자 소자는 일반적으로 실리콘을 주재료로 하는 전력 반도체 소자를 지칭합니다.

전력전자소자는 실리콘을 주재료로 하는 정보 반도체소자(또는 정보전자소자, IED)에 비해 다음과 같은 특징을 갖는다.

● 전력전자기기는 전력 처리 용량이 크지만 전력 손실이 크기 때문에 냉각용 라디에이터를 장착해야 한다.

● 전력 전자 장치는 종종 제어 신호를 제공하기 위해 정보 전자 장치를 필요로 합니다.

● 전력전자기기는 일반적으로 전력 소모를 줄이기 위해 증폭 상태가 아닌 스위칭 상태로 동작한다.

전력전자기기는 반도체의 특성상 동작 중에 필연적으로 일정한 전력 손실이 발생합니다. 이러한 전력 손실은 전기 에너지의 변환 효율을 감소시킬 뿐만 아니라 과열로 인해 전력 전자 장치에 영구적인 손상을 줄 수 있습니다. 전력 전자 장치의 주요 손실은 온 상태 손실, 오프 상태 손실 및 스위칭 손실로 나눌 수 있습니다. 온 손실은 온 전압 강하로 인한 손실이며, 전력 전자 장치의 스위칭 주파수가 높지 않은 경우 온 손실이 전체 손실의 높은 비율을 차지하게 됩니다. 오프 상태 손실은 오프 상태 누설 전류로 인한 손실이며 오프 상태 손실은 일반적으로 총 손실의 매우 작은 비율을 차지하며 종종 무시됩니다. 스위칭 손실은 전력 전자 장치의 스위칭 과정에서 발생하는 손실을 말하며 스위칭 손실은 스위칭 주파수의 영향을 크게 받습니다. 스위칭 주파수가 높을수록 전체 손실에는 스위칭 손실이 차지하는 비율이 커집니다.

사용되는 재료와 구조의 차이로 인해 다양한 유형의 전력 전자 장치의 성능이 완전히 다를 수 있습니다. 따라서 전력 전자 장치를 선택하기 전에 먼저 해당 범주와 특성을 이해하여 장점을 최대한 활용해야 합니다.

전력전자기기는 제어 정도에 따라 제어불능형, 반제 어협, 완전제어형으로 나눌 수 있다.

전력전자소자는 구동회로 신호에 따라 전류 구동형과 전압 구동형으로 나눌 수 있다. 전류 구동 장치의 작동 상태는 사이리스터, GTO, GTR 등과 같은 입력 전류에 의해 제어됩니다. 전압 구동 장치의 작동 상태는 입력 전압에 의해 생성되는 전계 효과에 의해 제어됩니다. MOSFET, JFET, IGBT 등.

전도 과정에 관여하는 캐리어에 따라 전력 전자 소자는 유니폴라 형과 바이 폴라 형으로 나눌 수 있다. 단극형 소자가 동작할 때는 MOSFET, JFET, SIT 등 한 종류의 캐리어(자유전자 또는 정공)만이 전도 과정에 참여한다. 밤이 폴라 형 소자가 동작할 때는 자유전자와 정공이 함께 전도에 관여한다. 사이리스터, GTO, GTR, IGBT, SITH, TRIAC, RCT, LTT 등과 같은 프로세스.

전압 국동 소자의 대부분은 단극형이고, 전류 국동 소자의 대부분은 바이 폴라 형이다. 전압 구동 장치는 일반적으로 높은 입력 임피던스, 낮은 구동 전력, 간단한 구동 회로 및 높은 작동 주파수의 특성을 가지고 있습니다. 전류 구동 장치에는 일반적으로 컨덕턴스 변조 효과가 있으므로 온 상태 전압 강하 및 전도 손실은 작지만 작동 주파수가 낮고 필요한 구동 전력이 크며 구동 회로가 더 복잡합니다.

§2. 제어할 수 없는 장치란 무엇입니까?

2.1 제어할 수 없는 장치 소개

제어 불가 장치는 제어 신호에 의해 온/오프할 수 없는 장치를 말하므로 구동 회로가 필요하지 않습니다. 제어 불가능한 소자는 일반적으로 파워 다이오드를 말하며 기본 구조와 작동 원리는 다이오드와 매우 유사합니다. 파워 다이오드는 넓은 면적의 PN 접합과 양쪽 끝의 리드선으로 캡슐화됩니다. 파워 다이오드는 모양에 따라 볼트형과 플랫형으로 나눌 수 있습니다. 전도 과정에 관여하는 캐리어에 따라 파워 다이오드는 유니폴라 파워 다이오드와 바이폴라 파워 다이오드로 나눌 수 있습니다. 파워 다이오드는 구조가 간단하고 가격이 저렴하여 다양한 분야의 전력기기에 널리 사용되고 있다. 특히 고속 회복 다이오드 및 쇼트키 배리어 다이오드는 저전압, 중간 주파수 및 고주파 필드의 정류 및 인버터에서 대체할 수 없는 위치에 있습니다. 모듈화 및 통합 기술의 발전으로 모듈식 전력 다이오드가 시장에서 점점 더 일반화되고 있습니다(더 많은 전력 다이오드 모듈을 보려면 클릭하십시오.)

2.2 파워 다이오드는 어떻게 작동합니까?

파워 다이오드의 본질은 P형 반도체와 N형 반도체가 접촉하여 형성되는 PN 접합입니다. 따라서 파워 다이오드의 작동 원리를 이해하기 위해서는 PN 접합의 기본 특성과 작동 원리를 이해할 필요가 있습니다.

2.2.1 PN 접합의 기본 구조

파워 다이오드는 P형 반도체와 N형 반도체로 구성된다. N형 반도체와 P형 반도체는 도핑된 진성 반도체로 구성됩니다. N형 반도체의 자유 전자 농도가 높습니다. P형 반도체의 정공 농도가 높다. P형 반도체와 N형 반도체 사이의 연결 영역을 PN 접합이라고 합니다. 자유 전자와 정공은 자유 캐리어(캐리어라고도 함)라고도 합니다. 반도체에서 자유전자의 이동과 재결합은 필연적으로 정공의 생성과 재결합으로 이어진다. 거시적 관점에서 볼 때 이 과정은 음전하를 띤 자유 전자와 양전하를 띤 정공이 동시에 반도체에서 반대 방향으로 이동하는 것과 비슷합니다. 반도체에서 자유전자와 정공의 움직임은 매우 빠르고 무작위적이어서 특정 자유전자나 정공의 궤적을 예측하고 특정 순간의 위치를 정확히 아는 것은 거의 불가능합니다. 그러나 많은 수의 정공과 자유 전자의 이동이 규칙이 없는 것은 아닙니다.

반도체의 대다수 캐리어는 고농도 영역에서 저농도 영역으로 확산됩니다. N 영역의 대다수 캐리어 자유 전자(nn)는 고농도 N 영역에서 PN 접합을 통해 확산됩니다. 저농도 P 영역으로; 동시에, P 영역의 다수 캐리어 홀(pp)은 고농도 P 영역에서 PN 접합을 통해 저농도 N 영역으로 확산됩니다. PN 접합 근처의 캐리어는 확산 이동으로 인해 고갈되고 이동할 수 없는 공간 전하(양이온 및 음이온)만 남게 되므로 이 영역을 공간 전하 영역(공핍 영역이라고도 함)이라고 합니다. 공간 전하 영역에는 자유롭게 움직이는 캐리어가 없기 때문에 절연체와 유사합니다. 공간 전하 영역의 공간 전하는 캐리어가 PN 접합을 통과하는 것을 방지하기 위해 내장 전기장을 생성합니다(내장 전기장은 PN 접합이 제조된 후 몇 나노초 내에 형성됨). 그럼에도 불구하고 PN 접합을 통과하고 반대 영역에서 소수 캐리어가 되는 캐리어는 여전히 매우 적습니다. 자유 전자는 P 영역(pn)에서 소수 캐리어가 됩니다. 구멍은 N 영역(np)에서 소수 캐리어가 됩니다. 이 현상을 양자 터널링 효과라고 합니다. 공간 전하 영역의 양쪽에서 캐리어 농도의 차이는 내장 전위차(내장 전위 또는 접촉 전위차라고도 함)를 생성합니다. 소수 캐리어는 저농도 지역으로 계속 확산될 것입니다. 소수 캐리어가 확산 및 재결합 과정에서 도달할 수 있는 평균 거리를 확산 길이라고 합니다. 확산 길이는 소수 캐리어 수명의 영향을 받습니다. 소수 캐리어 수명이 길수록 확산 길이가 길어집니다. 확산 영역의 가장자리에 도달하면 소수 캐리어는 PN 접합을 통과하고 내장 전기장의 작용에 따라 원래 영역으로 돌아갑니다.

* 단결정 반도체 및 다결정 반도체

단결정 반도체는 실리콘(Si), 게르마늄(Ge), 갈륨비소(GaAs) 등과 같은 순수한 화학 조성, 불순물 및 격자 결함이 없는 반도체, 즉 진성 반도체를 의미합니다. 단결정의 구조 반도체는 매우 규칙적이며 거시적 특성은 이방성입니다(다른 방향에서 물리적 특성이 다름). 단결정 반도체는 대부분의 반도체 장치의 재료입니다.

다결정 반도체는 방향이 다른 다수의 작은 단결정 반도체 입자로 구성된 반도체 재료를 말합니다. 다결정 반도체의 구조는 규칙성이 없으며 거시적 특성은 종종 등방성입니다(다른 방향에서 물리적 특성은 동일함). 다결정 반도체는 태양 전지, 액정 디스플레이 및 MOSFET용 게이트 재료용 협막 트랜지스터 스위치 매트릭스를 만드는 데 사용할 수 있습니다.

* 에너지 밴드 이론

에너지 밴드 이론은 양자 역학을 사용하여 고체 내부의 전자 운동을 연구하는 이론입니다. 에너지를 세로좌표로 하는 좌표계에서 결정에 있는 전자의 에너지는 수평선으로 나타낼 수 있습니다. 에너지가 클수록 선의 위치가 높아집니다. 특정 에너지 범위 내에서 서로 매우 가까운 에너지 준위가 에너지 밴드를 형성합니다. 에너지 대역에서 가장 높은 에너지 준위와 가장 낮은 에너지 준위 사이의 수직 거리를 에너지 대역 폭이라고 합니다. 에너지 밴드의 위치와 너비는 결정 유형(예: 금속, 반도체, 절연체), 온도 등에 영향을 받습니다. 반도체의 에너지 밴드는 그림 3.2a에 나와 있습니다.

Full Band: T = 0K일 때 전자가 완전히 차지하는 에너지 밴드를 말합니다. 풀 밴드의 전자는 원자가 전자(즉, 결정 원자의 원자가 결합에 묶여 자유롭게 움직일 수 없는 전자)이므로 전도성이 없습니다.

Empty Band: T = 0K일 때 전자가 차지하지 않는 에너지 밴드를 말한다. 빈 밴드에는 전자가 없으므로 전도성이 없습니다. 빈 밴드는 전자가 있을 때 전도 밴드가 됩니다.

Conduction Band: T > 0K. 전도대의 전자는 자유전자이므로 전도도가 있습니다.

Valence Band: T > 0K. 원자가 밴드의 전자는 원자가 전자이므로 전도성이 없습니다.

Forbidden Band: 가전자대의 상단과 전도대의 하단 사이의 에너지 범위를 나타냅니다. 금지대에는 공유 전자(즉, 결정의 여러 원자가 공유하는 전자)의 에너지 준위가 없지만, 비공유 전자(즉, 불순물 및 결함에 편재된 전자)의 에너지 준위는 있습니다. 금지 대역 폭(band gap)은 원자가 전자의 속박 정도 또는 원자가 결합의 강도, 즉 고유 여기에 필요한 최소 평균 에너지를 반영합니다. 금단의 중간선은 페르미 준위이다.

일반적인 금속 재료의 밴드 갭은 일반적으로 매우 작고(전도대와 가전자대가 서로 겹치기도 함), 전자는 실온에서 쉽게 에너지를 얻고 전도대로 전이할 수 있으므로 전도성이 강합니다. 절연 물질의 밴드 갭은 일반적으로 매우 크고(보통 9전자볼트 또는 9eV보다 큼), 전자가 전도대로 전이되기 어려워 전도도가 매우 낮습니다. 반도체 재료의 밴드갭은 도체와 절연체 사이에 있으므로(예를 들어 상온에서 약 1-3 eV, 게르마늄의 밴드갭은 0.67 eV, 실리콘의 밴드갭은 1.12 eV) 적당한 에너지를 주면 된다. 여기(자유 전자와 정공을 생성하기 위해 원자가 전자가 전도대로 전이되도록 원자가 결합을 끊음) 또는 밴드 갭 변경(전자 전이에 필요한 에너지 감소)은 반도체를 전도성으로 만들 수 있습니다.

* 고유 여기 및 자유 캐리어

고유 여기(intrinsic excitation)는 특정 여기 조건을 부여함으로써 고유 반도체의 전자가 낮은 에너지 대역(full band 또는 valence band)에서 더 높은 에너지 대역(empty band 또는 conduction band)으로 금지 대역을 건너 자유 전자가 되는 것을 의미합니다. . 진성 반도체의 전도대의 자유 전자는 고체 전체에서 자유롭게 이동할 수 있지만 고체 밖으로 나갈 수 없는 고체의 대략적인 자유 전자를 의미한다는 점에 유의해야 합니다. 정공이라고 불리는 낮은 에너지 대역에 전자가 부족하여 양전하를 띤 공석이 형성됩니다. 전도대에 있는 자유전자와 가전자대에 있는 정공을 총칭하여 전자-정공 쌍이라고 합니다. 진성반도체에서는 진성여기에 의해 생성된 자유전자와 정공이 자유롭게 이동할 수 있어 자유캐리어(free carrier)라고 하며 농도는 서로 같으며 온도가 상승하면 농도가 기하급수적으로 증가한다. 자유 전자와 정공의 방향성 이동은 전자 흐름과 정공 흐름을 형성합니다. 전도대의 자유 전자는 정공으로 떨어져 전자-정공 쌍이 사라집니다. 이 과정을 재조합이라고 합니다. 재결합 중에 생성된 에너지는 전자기 복사(광자 방출) 또는 격자의 열 진동(포논 방출)의 형태로 방출됩니다. 특정 온도에서 전자-정공 쌍의 생성과 재결합이 동시에 존재하며 동적 평형에 도달합니다. 이때, 진성 반도체는 일정한 캐리어 농도를 가지므로 일정한 전기 전도도를 갖는다. 고유 여기를 통해 더 많은 전자-정공 쌍이 생성되어 캐리어 농도가 증가하여 반도체의 전도도를 효과적으로 높일 수 있습니다. 이 원리에 따르면, 반도체 서미스터, 반도체 포토레지스터 등의 반도체 소자를 제조할 수 있다. 진성 반도체는 상온에서 전도도가 작고 캐리어 농도가 온도 변화에 민감하여 온도를 통해 반도체의 반도체 특성을 효과적으로 제어하기 어렵다.

고유 가진 방법은 일반적으로 고유 열 여기, 고유 광 여기 및 충격 이온화 고유 여기로 나눌 수 있습니다.

고유 열 여기(Intrinsic Thermal Excitation): 온도가 증가함에 따라 분자의 열 운동에 의해 방사되는 적외선 광자를 말하며, 이는 원자가 전자가 원자가 결합의 속박에서 벗어나 자유 전자가 되기에 충분한 에너지를 얻도록 합니다. 고유 열 여기에 필요한 에너지는 밴드 갭과 같습니다. 충분한 캐리어가 전도대로 전환되도록 하려면 매우 높은 온도가 필요하기 때문에 실온에서 열 여기 효율은 일반적으로 매우 제한적입니다.

고유광 여기(Intrinsic Light Excitation): 빛(일반적으로 가시광선 또는 자외선 참조)에 의해 방출되는 광자를 말하며, 원자가 전자가 원자가 결합의 속박에서 벗어나 자유 전자가 되기에 충분한 에너지를 얻습니다. 고유 광 여기에 필요한 에너지는 고유 열 여기보다 큽니다. 가시광선의 광자는 일반적으로 열 운동에 의해 생성되는 적외선 광자보다 높은 에너지를 가지므로 고유광 여기 후 전자의 에너지는 일반적으로 전도대에서 더 높은 위치에 위치합니다. 광자의 운동량은 무시할 수 있기 때문에 고유 광의 여기가 전자의 운동량을 변화시키지 않으므로 이 과정을 수직 전이라고도 합니다. 그러나 포논(결정격자의 단순 고조파 진동)이 관련되어 있으면 전자의 운동량이 변경되므로 수직이 아닌 천이라고도 합니다.

충격 이온화 고유 여기: 고에너지 전자(즉, 전기장에 의해 가속된 자유 전자)에 의해 원자가 전자가 충돌 및 이온화되어 자유 전자가 되는 것을 말합니다. 충격 이온화 고유 가진에 필요한 평균 에너지는 밴드 갭의 약 1.5배입니다. 충격 이온화의 고유 여기에 의해 생성된 전자는 이온화된 전자이며, 이는 고체를 떠날 수 있는 진정한 자유 전자이며 그 에너지는 전도대에서 가장 높은 에너지 준위를 갖는 자유 전자를 초과합니다.

* 페르미 준위 및 페르미-디랙 분포

페르미 준위는 어떤 온도에서도 전자가 차지할 확률이 50%인 에너지 준위입니다. 페르미 준위보다 낮을수록 거리가 멀수록 전자가 차지할 가능성이 커집니다. 페르미 준위 이상이면 거리가 멀수록 전자가 차지할 가능성이 적습니다. 반도체, 특히 진성 반도체의 경우 페르미 준위는 금지대의 중간 선에 있습니다. 온도 T = 0K일 때, 전체 대역은 전자로 채워지고(전자 점유 확률은 1), 빈 대역에는 전자가 전혀 없습니다(전자 점유 확률은 0), 페르미 준위는 정확히 중간에 있습니다. 금단의 선(전자 점유 확률은 1/2). 온도가 올라가도 T> 0K에서 고유한 여기가 전자-정공 쌍을 생성하지만 전도대에서 증가된 전자의 수는 가전자대에서 감소한 전자의 수와 같기 때문에 페르미 준위는 여전히 금지대의 중간선에 있습니다. 전자 점유 확률은 1/2)입니다. 따라서 진성 반도체의 페르미 준위의 위치는 온도에 따라 변하지 않고 항상 금단의 중간선에 있다. 전자의 페르미-디랙 분포는 그림 3.2b와 같이 페르미 준위와 온도에서 계산할 수 있습니다.

* 반도체 도핑

일반적으로 진성 반도체는 전도성을 높이기 위해 새로운 에너지 수준을 도입하기 위해 도핑됩니다. 도핑된 반도체는 외부 영향(예: 빛, 온도 상승 등)에 더 취약합니다.

인 원소(또는 안티몬 원소)로 실리콘 결정(또는 게르마늄 결정)을 도핑함으로써, 인 원자(또는 안티몬 원자)는 실리콘 원자의 위치를 차지할 것이다. 그런 다음 전도 대역에 매우 가까운 금지 대역의 위치에 전체 에너지 준위 세트가 추가됩니다. 이러한 에너지 준위의 전자는 전도대로 쉽게 전이되어 자유 전자가 될 수 있습니다. 따라서 인 원소(또는 안티몬 원소)를 도너 불순물(또는 N형 불순물)이라 하고, N형 불순물이 도핑된 반도체를 N형 반도체라고 한다.

실리콘 결정(또는 게르마늄 결정)에 붕소 원소(또는 인듐 원소)를 도핑함으로써 붕소 원자(또는 인듐 원자)가 실리콘 원자의 위치를 차지하게 됩니다. 그런 다음 일련의 빈 에너지 준위가 원자가 대역에 매우 가까운 금지 대역의 위치에 추가됩니다. 가전자대의 전자는 이러한 에너지 준위로 쉽게 전환되어 가전자대에 정공을 남길 수 있습니다. 따라서 붕소 원소(또는 인듐 원소)를 억셉터 불순물(또는 P형 불순물)이라고 하고, P형 불순물이 도핑된 반도체를 P형 반도체라고 한다.

2.2.2 PN 접합의 단방향 전도도

파워 다이오드의 작동 원리의 본질은 PN 접합의 단방향 전도성입니다. 일정한 외부 조건(온도, 복사열 등)의 경우 외부 회로는 파워 다이오드의 작동 중에 소비되는 캐리어를 보충하므로 파워 다이오드의 전도도는 주로 내부 캐리어 농도에 영향을 받습니다.

순방향 전도 상태: 순방향 바이어스 전압이 전원 다이오드에 인가되면 다수 캐리어가 PN 접합에 더 가깝게 이동하여 공간 전하 영역이 좁아지고 내장된 전기장이 약해지지만 PN 접합은 여전히 유지됩니다. 동적 평형 상태. 순방향 바이어스 전압이 내장 전기장보다 클 때만 동적 평형이 깨질 수 있으며 드리프트 전류의 반대 방향으로 중첩 전기장이 생성됩니다. 확산 전류 ID는 드리프트 전류 Id보다 큽니다. PN 접합을 통해 흐르는 전류는 순방향 전류 IF입니다. 내장된 전위차로 인해 파워 다이오드가 순방향 전도 상태일 때 양단에 온 상태의 전압 강하가 발생하여 파워 다이오드가 낮은 임피던스 상태를 나타냅니다. 파워 다이오드의 온 전압 강하는 고정된 값이 아니라 흐르는 전류에 비례합니다.

역 차단 상태: 역 바이어스 전압이 전력 다이오드에 인가되면 다수 캐리어가 PN 접합에서 멀어져 공간 전하 영역이 넓어지고 내장 전기장이 향상됩니다. PN 접합의 동적 평형이 깨지고 드리프트 전류와 같은 방향으로 중첩된 전기장이 생성됩니다. 드리프트 전류 Id는 확산 전류 ID보다 큽니다. PN 접합을 통해 흐르는 전류는 역포화 전류 Isat입니다. 소수 캐리어의 수가 너무 적기 때문에 파워 다이오드의 역 포화 전류는 일반적으로 무시할 수 있으므로 파워 다이오드가 높은 임피던스 상태를 나타냅니다.

역 항복 상태: 전력 다이오드의 역 바이어스 전압이 특정 임곗값까지 계속 증가하면 전력 다이오드의 캐리어 수가 급격히 증가하여 역전류 IR이 크게 증가합니다. 역 항복 상태에서 파워 다이오드는 임피던스가 없는 상태를 나타내며 역 전류 IR 및 역 전압 UR은 모두 매우 큽니다. PN 접합의 역 항복은 주로 눈사태 항복과 제너 항복으로 나뉩니다. 이러한 고장은 모두 PN 접합의 온도를 증가시키고 결국 열 고장으로 이어져 PN 접합에 영구적인 손상을 초래합니다. 냉각 조치가 충분히 이루어지면 전원 다이오드가 역방향으로 고장 나더라도 PN 접합이 파괴되지 않으면 역 전압을 제한하거나 닫은 후에도 PN 접합을 여전히 원래 상태로 복원할 수 있습니다.

* 확산 전류 및 드리프트 전류

확산 운동은 고농도 영역에서 저농도 영역으로 다수 캐리어의 이동을 나타냅니다. 확산 운동은 농도 구배에 의해 결정됩니다. 드리프트 모션은 내장된 전기장의 작용에 따라 소수 캐리어가 원래 영역으로 돌아가는 움직임을 나타냅니다. 드리프트 모션은 내장된 전기장에 의해 결정됩니다. 확산 운동과 드리프트 운동은 PN 접합에서 캐리어의 기본 운동입니다. 확산 운동에 의해 생성된 전류를 확산 전류 ID라고 하고, 드리프트 운동에 의해 생성된 전류를 드리프트 전류 Id라고 합니다. 인가전압이 없을 때(또는 순방향 바이어스 전압이 내장 전기장보다 작음), 확산 운동으로 인해 내장 전기장이 강화되고 드리프트 전류가 증가합니다. 드리프트 동작으로 인해 내장 전기장이 약해지고 확산 전류가 증가합니다. 마지막으로, 확산 전류는 드리프트 전류와 같으며 PN 접합은 총 전류가 0인 동적 평형 상태가 됩니다.

* 눈사태 고장 및 제너 고장

눈사태 고장 은 일반적으로 넓은 공핍층이 있는 저농도 도핑 PN 접합에서 발생합니다. 넓은 공핍층으로 인해 역 바이어스가 클 때 반도체의 자유 전자는 전개력 하에서 지속적으로 가속되어 많은 운동 에너지를 얻습니다. 이 고에너지 전자는 원자가 전자와 충돌하여 원자가 결합의 속박에서 벗어나 새로운 전자-정공 쌍을 생성합니다. 이렇게 새로 생성된 자유전자는 전기력의 작용으로 이 과정을 계속 반복하여 반도체의 자유 캐리어를 눈사태처럼 급격히 증가시켜 드리프트 전류를 급격히 증가시킨다. 눈사태 항복의 본질은 충격 이온화 여기이므로, 눈사태 항복 전압은 일반적으로 높습니다(일반적으로 6V 이상). 애벌랜치 항복 전압은 온도가 증가함에 따라 증가하는데, 그 이유는 주로 온도가 증가함에 따라 캐리어의 불규칙한 열 운동이 증가하기 때문입니다. 따라서 캐리어가 방향 가속 운동을 하도록 충분히 큰 전기장을 제공하려면 더 큰 역전압이 필요합니다.

제너 항복은 일반적으로 좁은 공핍층이 있는 고도로 도핑 된 PN 접합에서 발생합니다. 공핍층이 좁기 때문에 자유전자가 가속될 공간이 충분하지 않아 애벌 런치 브레이크 다운이 일어나지 않는다. 동시에 좁은 공핍층으로 인해 역 바이어스가 크지 않더라도 PN 접합에서 여전히 강한 전기장이 생성되어 원자가 결합에서 전자를 끌어내고 새로운 전자-정공 쌍을 생성할 수 있습니다. 이 현상을 장 유도 여기라고도 합니다. 자기장 유도 여기(field-induced excitation)는 반도체의 캐리어 수를 크게 증가시켜 드리프트 전류를 크게 증가시킵니다. 제너 항복 전압은 일반적으로 낮습니다(일반적으로 4V 미만). 제너 항복 전압은 온도가 증가함에 따라 감소합니다. 주로 원자가 결합의 전자가 온도가 증가함에 따라 더 활성화되기 때문에 전기력이 전자를 더 쉽게 끌어낼 수 있기 때문입니다.

2.2.3 PN 접합의 커패시턴스 효과

PN 접합의 전하량은 인가전압에 따라 변화하여 정전 용량 효과를 나타냅니다. 이 커패시턴스를 접합 커패시턴스 CJ(차동 커패시턴스라고도 함)라고 합니다. 다른 생성 메커니즘과 기능에 따라 접합 커패시턴스 CJ는 장벽 커패시턴스 CB와 확산 커패시턴스 CD로 나눌 수 있습니다. , 계산식 CJ=CB+CD를 따릅니다. 배리어 커패시턴스 왓 확산 커패시턴스는 모두 비선형 커패시턴스입니다.

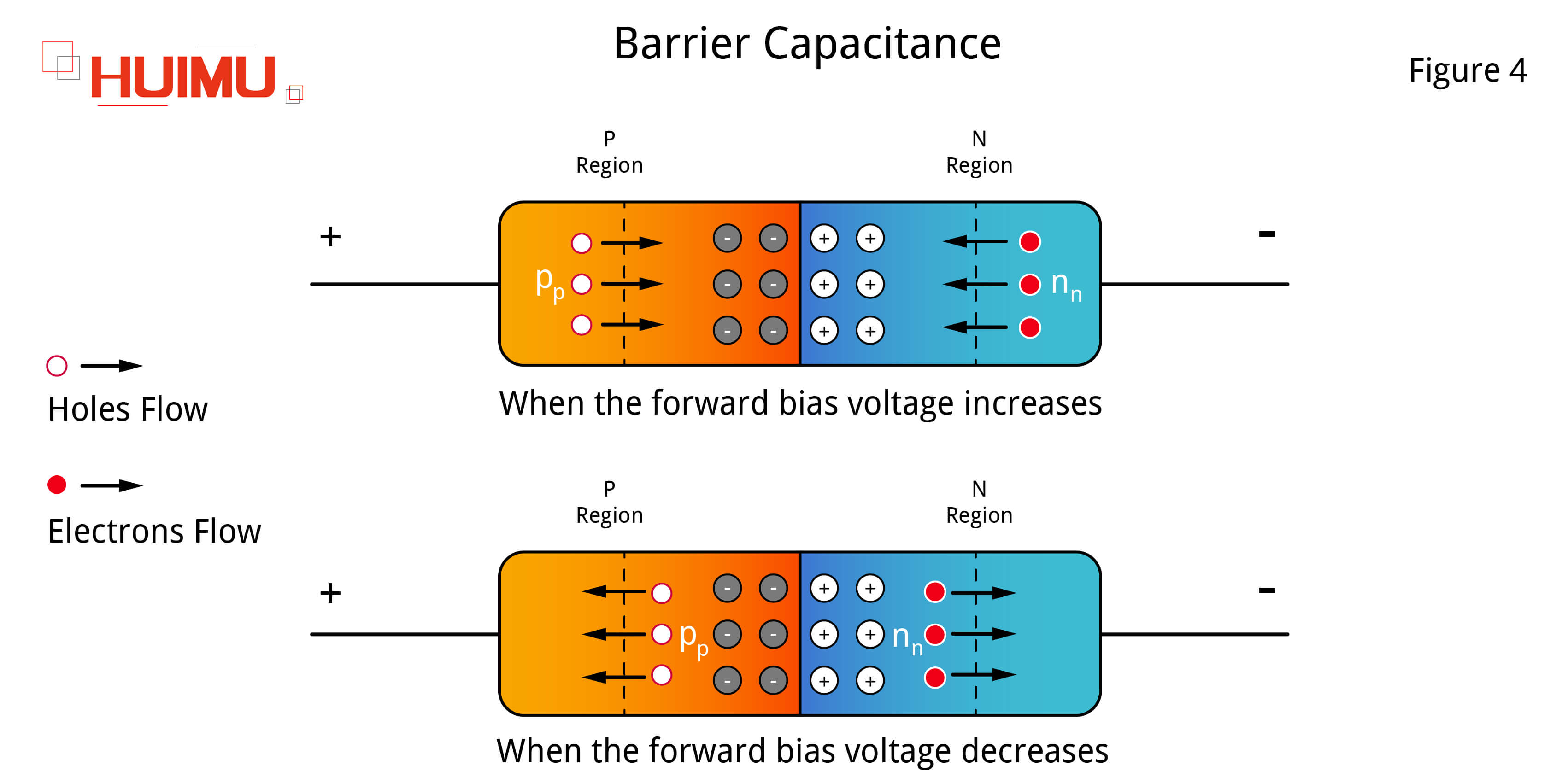

1- 배리어 커패시턴스

공간 전하 영역(공핍층)의 좁은 이온층은 장벽 영역을 형성합니다. 인가된 바이어스 전압에 따라 장벽 영역의 공간 전하 수는 커패시터의 충방전 효과와 동일하게 변합니다. 순방향 바이어스 전압이 증가하면 장벽 영역이 감소하여 자유 전자 또는 장벽 영역에 구멍; 순방향 바이어스가 감소하면 장벽 영역이 증가하며 이는 장벽 영역에서 자유 전자 또는 정공을 빼내는 것과 같습니다. 배리어 영역의 등가 커패시턴스를 배리어 커패시턴스 CB라고 합니다. 인가된 바이어스 전압의 주파수가 높으면 장벽 커패시턴스 희 영향이 더 분명해집니다. 저주파 동작이든 고주파 동작이든 상관없이 배리어 커패시턴스는 반도체 장치의 단방향 전도도를 저하시키거나 심지어 작동하지 않을 수도 있다. 실제로 반도체 소자의 최대 동작 주파수는 종종 배리어 커패시턴스 애 의해 결정된다. 장벽 커패시턴스는 다수 캐리어(pp 및 nn)와 관련된 커패시턴스 효과이며 순방향 바이어스와 역방향 바이어스 모두 무시. 순방향 바이어스에서는 순방향 전압이 낮을 때 배리어 커패시턴스가 확산 커패시턴스 보답 훨씬 크므로 배리어 커패시턴스가 접합 커패시턴스 CJ ≈ CB의 주요 구성 요소입니다.

2- 확산 커패시턴스

PN 접합이 순방향 바이 어스되면 내장 전기장이 약해지고 소수 캐리어의 드리프트 모션이 약해집니다. 확산 전류는 드리프트 전류보다 큽니다. 따라서 반대 영역으로 확산되는 캐리어는 장벽 경계에 축적되어 특정 농도의 비평형 소수 캐리어(pn 및 np)를 형성합니다. PN 접합에 가까울수록 농도가 높아집니다. PN 접합에서 멀어질수록 농도가 낮아집니다. 이러한 비평형 소수 캐리어의 전하량은 순방향 바이어스에 따라 변하는데, 이는 커패시터의 충전 및 방전 효과와 동일합니다. 순방향 바이어스가 증가하면 비평형 소수 캐리어가 증가하며, 이는 다음과 같습니다. 커패시터 충전; 순방향 바이어스가 감소하면 비평형 소수 캐리어가 감소하며 이는 커패시터의 방전과 동일합니다. 장벽 영역의 경계에서 등가 커패시턴스를 확산 커패시턴스 CD라고 합니다. 확산 커패시턴스는 저주파에서 작동할 때 PN 접합의 스위칭 속도에 큰 영향을 미치며 고주파에서 작동할 때 무시할 수 있습니다. 순방향 바이어스에서 순방향 전압이 높으면 확산 커패시턴스가 배리어 커패시턴스 보답 훨씬 크기 때문에 확산 커패시턴스가 접합 커패시턴스 희 주성분인 CJ ≈ CD . 역 바이어스에서는 비평형 소수 캐리어가 너무 적고 확산 커패시턴스를 무시할 수 있으므로 장벽 커패시턴스가 접합 커패시턴스 CJ ≈ CB의 주요 구성 요소입니다.

2.3 파워 다이오드의 주요 파라미터

1- 최대 순방향 평균 전류 IFM(AV)

최대 순방향 평균 전류 IF(AV)는 전력 다이오드의 정격 전류로, 아래에서 전력 다이오드를 통해 흐를 수 있는 최대 전력 주파수 반파 사인 전류의 평균값을 나타냅니다. 지정된 케이스 온도 TC 및 방열 조건. IF(AV)를 초과하면 다이오드가 소손됩니다. 일부 파워 다이오드의 파형은 반드시 반 정현파가 아니며 일부 파워 다이오드는 저항 특성이 없기 때문에 IF(AV)는 전류의 열 효과에 따라 정의됩니다. 즉, , 동일한 실횻값의 원리에 따라 유사한 발열을 갖는 저항기를 찾으십시오. 방열 조건이 전류를 견디는 파워 다이오드의 능력에 영향을 미친다는 점을 고려하면 방열 문제로 인한 파워 다이오드의 손상을 방지하기 위해 일정한 여유를 두는 것이 좋습니다.

2- 임계 전압 UTO

임계 전압 UTO(데드 존 전압이라고도 함)은 전원 다이오드가 켜질 수 있는 가장 낮은 순방향 전압입니다. 임계 전압은 파워 다이오드의 가장 낮은 순방향 전압 강하입니다. 게르마늄 결정의 임계 전압은 약 0.1V입니다. 실리콘 결정의 문턱 전압은 약 0.5V입니다.

3- 온 상태 전압 강하 UCO

온 상태 전압 강하 UCO(전도 전압이라고도 함)는 전원 다이오드가 켜져 있고 안정적으로 작동할 때 순방향 전압 강하입니다. 이상적으로는 전원 다이오드의 온 상태 전압 강하는 내장 전위와 동일합니다. 내장 전위는 반도체 도핑 정도와 관련이 있으며 밴드 갭의 절반과 거의 같습니다. 파워 다이오드의 온 상태 전압 강하는 흐르는 전류에 비례합니다. 게르마늄 결정의 온 상태 전압 강하는 일반적으로 약 0.1-0.3V입니다. 실리콘 결정의 온 상태 전압 강하는 일반적으로 약 0.5-0.8V입니다.

4- 최대 순방향 전압 강하 UFM

최대 순방향 전압 강하 UFM은 지정된 온도에서 최대 순방향 평균 전류 IFM(AV)에 해당하는 순방향 전압 강하입니다.

5- 역포화 전류 Isat

적절한 역 전압이 인가되면 역포화 전류 Isat라고 하는 매우 작은 누설 전류가 생성됩니다. 역포 회전류는 소수 캐리어의 드리프트 운동에 의해 발생하므로 온도의 영향을 크게 받습니다.

6- 역 반복 피크 전압 URRM

역반복 피크 전압 URRM(최대 역전압 URM이라고도 함)은 파워 다이오드의 정격 전압으로, 이는 전원 다이오드는 반복적으로 적용될 수 있습니다. 이 값을 초과하면 파워 다이오드가 역전되어 파손됩니다. 회로의 과전압 및 기타 요인을 고려하면 파워 다이오드를 사용할 때 일반적으로 이중 마진이 있어야 합니다. 예를 들어 정격 전압이 1000V인 파워 다이오드는 500V 파워 다이오드로만 사용할 수 있습니다.

7- 역 복구 시간 trr

역 회복 과정은 파워 다이오드의 커패시턴스 효과에 의해 발생합니다. 스위치가 온 상태에서 오프 상태로 전환될 때 파워 다이오드는 역전류를 차단하기 전에 접합 커패시턴스 애 저장된 전하를 방출해야 합니다. 이 방전 시간을 역 회복 시간 trr, 즉 순방향 전도 전류가 0인 시점부터 완전히 턴 오프 상태가 될 때까지의 시간이라고 합니다. 사양이 다른 파워 다이오드는 역회복 시간이 다르기 때문에 회로 설계 시 충분히 고려하여야 합니다. 그렇지 않으면 불필요한 문제가 발생할 수 있습니다. 예를 들어, 파워 다이오드의 역회복 시간은 Trr입니다. T1 주기(T1<Trr)의 연속 PWM 파가 파워 다이오드를 통과하면 PWM 파는 파워 다이오드가 역 바이 어스될 때 차단됩니다.

8- 최대 작동 접합 온도 TJM

접합 온도 TJ는 PN 접합의 평균 온도를 나타냅니다. 최대 작동 접합 온도 TJM은 PN 접합이 손상 없이 견딜 수 있는 최고 평균 온도를 나타냅니다(일반적으로 게르마늄 트랜지스터의 최고 접합 온도는 약 75°C이고 실리콘의 최고 접합 온도는 트랜지스터는 약 150°C입니다). 온도는 파워 다이오드의 작동 특성에 매우 큰 영향을 미치므로 과열로 인해 파워 다이오드가 손상되지 않도록 충분한 방열 조건을 제공해야 합니다.

9- 최대 작동 주파수 fM

최대 작동 주파수 fM은 다이오드의 상위 턴 오프 주파수입니다. 주파수가 너무 높으면 전력 다이오드가 용량 효과로 인해 역전류를 차단하는 기능을 쉽게 잃게 됩니다. 동시에 주파수가 너무 높으면 온 상태의 소비 전력 증가로 인해 파워 다이오드가 연소됩니다.

10- 서지 전류 IFSM

서지 전류 IFSM은 전력 다이오드가 견딜 수 있는 하나 이상의 전력 주파수 주기의 최대 연속 과전류를 나타냅니다.

2.4 파워 다이오드의 기본 특성

2.4.1 파워 다이오드의 정적 특성

파워 다이오드의 정적 특성은 주로 그림 6과 같이 파워 다이오드의 볼트-암페어 특성 곡선을 나타냅니다.

파워 다이오드의 양단에 순방향 바이어스 전압을 인가하면 파워 다이오드가 즉시 켜지지 않습니다. 순방향 전압이 파워 다이오드의 임계 전압 UTO보다 클 때만 파워 다이오드가 켜집니다. 이때 순방향 전류 IF가 크게 증가하기 시작하여 파워 다이오드가 안정적인 전도 상태가 될 때까지 다이오드의 전도 전압이 UCO. 순방향 전류가 IFM에 도달하면 해당 전압 강하는 UFM이 되며 과도한 전류로 인해 파워 다이오드가 소손됩니다.

파워 다이오드의 양단에 역 바이어스 전압을 인가하면 파워 다이오드는 전도되지 않고 작은 일정한 값의 전류, 즉 역 누설 전류가 생성됩니다. 역전압이 파워 다이오드의 역 UBR에 도달하면 파워 다이오드가 역으로 분해되고 이때 역전류가 매우 커지게 됩니다.

2.4.2 파워 다이오드의 동적 특성

파워 다이오드의 동적 특성은 스위칭 특성, 즉 온 상태에서 오프 상태로 전환되는 동안 파워 다이오드의 전압-전류 특성을 말합니다. 접합 커패시턴스 때문에 파워 다이오드의 전압-전류 특성은 시간에 따라 변합니다.

1- 켜기 프로세스

턴 온 프로세스에서 파워 다이오드의 동적 특성은 그림 7에 나와 있습니다. 전압이 제로 바이어스에서 순방향 바이어스로 변경되면 파워 다이오드의 순방향 전류 IF가 0에서 증가합니다. IF1. 큰 di/dt로 인해 라인 인덕턴스의 작용으로 파워 다이오드의 양단에서 순방향 피크 전압 UFP가 생성됩니다. 일정 시간이 지나면 순방향 전압 UF가 UFP에서 안정적인 전압 UF1(즉, 온 상태 전압 강하). 이 과정에서 순방향 전류가 0에서 IF1까지 상승하는 시간을 순방향 회복 시간 tfr이라고 합니다.

2- 종료 프로세스

턴 오프 과정에서 파워 다이오드의 동적 특성은 그림 8과 같습니다. 접합 커패시턴스 론 인해 순방향 바이어스가 역방향 바이어스로 변환되더라도 파워 다이오드는 즉시 꺼지지 않지만 역 차단 기능을 회복하는 데 시간이 걸립니다.

파워 다이오드가 tF에서 순방향 바이어스에서 역방향 바이어스로 전환되면 순방향 전류 IF가 급격히 감소하고 t0에서 0으로 떨어지고 diF/dt가 크다. t0에서 t1까지 전류는 사라지지 않을 뿐만 아니라 역전류 IR이 되어 최대값 IRP에 도달할 때까지 급격히 증가합니다. 이 기간을 지연 시간 td라고 합니다. t1에서 t2까지 역전류는 매우 작은 값으로 급격히 떨어지기 시작합니다. 이 기간을 하강 시간 tf라고 합니다. t2부터 역방향 전류는 0으로 떨어질 때까지 천천히 감소하기 시작합니다(사실 역 누설 전류는 여전히 매우 작음). t0에서 t2까지의 시간을 역 회복 시간 trr이라고 하며, 이 시간 동안 파워 다이오드가 역전도됩니다. 역 회복 시간 trr은 파워 다이오드의 동작 주파수를 결정합니다. 외부 회로의 작동 주파수가 너무 높으면 역방향 바이어스 시 파워 다이오드가 역 차단 상태에 들어갈 수 없으며 역전류가 크게 발생합니다. 이는 파워 다이오드가 역 차단 능력을 잃는 것과 같습니다.

역방향 전류가 최대값으로 상승하기 전에 파워 다이오드 양단의 전압은 온 상태의 전압 강하 UF1에서 0으로 급격히 떨어집니다. 동시에 tf는 일반적으로 매우 짧기 때문에 diR/dt는 매우 큽니다. 라인 인덕턴스의 작용으로 파워 다이오드의 양단에서 역첨두 전압 URP가 빠르게 생성되다가 안정된 값 UR1까지 떨어지기 시작한다. 역 피크 전압은 일반적으로 매우 크며 파워 다이오드를 파괴할 수 있습니다. 따라서 trr에서 tf의 비율을 높이면 역 피크 전압을 줄이는 데 도움이 됩니다. 회복 계수(Sr=tf/td)는 일반적으로 파워 다이오드의 역회복 특성의 부드러움을 표현하는 데 사용됩니다.

2.5 파워 다이오드의 주요 유형

1- 범용 다이오드

정류기 다이오드라고도 하는 범용 다이오드(GPD)는 긴 회복 시간, 높은 순방향 전류 정격 및 역방향 전압 정격을 갖습니다. 주로 낮은 스위칭 주파수(1kHz 이하)의 정류회로에 사용되며 일반적으로 중주파 및 고주파수 회로에는 사용할 수 없습니다.

2- 빠른 복구 다이오드

FRD(Fast Recovery Diode)의 내부 구조는 범용 다이오드와 다릅니다. P-I-N 구조를 형성하기 위해 P형과 N형 실리콘 재료 사이에 기본 영역 I을 추가합니다. 베이스 영역이 매우 얇고 역 회복 전하가 적기 때문에 trr 및 과도 순방향 전압 강하를 크게 감소시킬 뿐만 아니라 역전압 내성 능력을 향상시킵니다. 고속 회복 다이오드의 회복 시간은 매우 짧고(trr>100ns, 일반적으로 수백 ns) 순방향 전압 강하는 약 0.6V이며 순방향 전류는 수 암페어에서 수천 암페어입니다. , 역 피크 전압은 수백에서 수천 볼트에 이를 수 있습니다. 고속 복구 에피택시 다이오드(FRED)라고도 하는 초고속 복구 다이오드는 역 복구 전하가 더 감소하므로 복구 시간이 더 짧습니다(trr<100ns, 최저 20 ~30ns). 초고속 회복 다이오드의 순방향 전압 강하는 또한 매우 낮지만(약 0.9V), 역방향 내전압 성능은 일반적으로 높지 않습니다(1200V 미만).

3- 쇼트키 배리어 다이오드

쇼트키 배리어 다이오드(SBD)는 금속과 반도체가 접촉하여 형성된 배리어를 기반으로 하는 일종의 파워 다이오드입니다. 범용 다이오드 및 고속 회복 다이오드와 비교하여 쇼트키 배리어 다이오드는 역 회복 시간이 짧고 순방향 전압 오버슈트가 뚜렷하지 않으며 역 저항 전압이 높지만 역 누설 전류가 크다는 장점이 있습니다. 쇼트키 배리어 다이오드의 순방향 전압 강하는 역방향 내전압의 영향을 받으며 역방향 내전압이 증가하면 순방향 전압 강하는 크게 증가합니다. 그러나 역방향 내전압이 낮을 때 쇼트키 배리어 다이오드의 순방향 전압 강하는 범용 다이오드 및 고속 회복 다이오드에 비해 현저히 낮아 스위칭 손실과 온 상태 손실이 매우 낮습니다. 따라서 쇼트키 배리어 다이오드는 일반적으로 200V 미만의 정류 회로에 사용됩니다. 그러나 쇼트키 배리어 다이오드는 온도에 매우 민감하므로 작동 온도를 엄격하게 제한해야 합니다.

§3. 트랜지스터 란 무엇입니까?

반지에 어 소자와 완전제어 소자를 소개하기 전에 BJT(Bipolar Junction Transistor)에 대해 간략히 소개할 필요가 있다.

3.1 트랜지스터 소개

트랜지스터(반도체 트랜지스터 또는 Bipolar Junction Transistor, BJT라고도 함)는 3개의 단자와 2개의 PN 접합이 있는 바이폴라 장치입니다. 트랜지스터는 반도체 소자의 기본 부품이자 핵심 부품 중 하나입니다. 1940년대에 탄생한 이래 트랜지스터는 전자 회로의 구조를 완전히 바꾸어 반도체 혁명을 일으켰으며 집적 회로와 대규모 집적 회로의 출현을 촉진했습니다. 트랜지스터는 전류 증폭 기능이 있어 베이스 전류의 아주 작은 변화로 컬렉터 전류의 큰 변화를 제어할 수 있어 전자 회로에서 무접점 스위치로 많이 사용된다. 트랜지스터의 스위칭 주파수가 높고 기계적 수명이 없으므로 전자기 릴레이 및 기계식 스위치에 비해 이점.

3.2 트랜지스터는 어떻게 작동합니까?

3.2.1 트랜지스터의 기본 구조

트랜지스터는 파워 다이오드보다 PN 접합이 하나 더 있는 3층 반도체 구조입니다. 이 밀접하게 배치된 두 개의 PN 접합은 트랜지스터를 서로 다른 영역과 도핑 농도를 가진 세 부분으로 나눕니다. 기본 영역은 매우 얇습니다(3- 30μ m) 도핑 농도가 낮습니다. 이미터 영역의 면적이 작고 도핑 농도가 높습니다. 컬렉터 영역의 면적이 크고 도핑 농도가 낮습니다. 컬렉터 영역과 베이스 영역 사이의 PN 접합을 컬렉터 접합 J1라고 합니다. 이미터 영역과 베이스 영역 사이의 PN 접합을 이미터 접합 J2라고 합니다.

트랜지스터는 재료에 따라 실리콘 트랜지스터와 게르마늄 트랜지스터로 나눌 수 있습니다. 도핑 구성에 따라 트랜지스터는 PNP 트랜지스터와 NPN 트랜지스터로 나눌 수 있습니다. 순방향 바이어스에서 PNP 트랜지스터의 이미 터 영역은 정공을 방출하고 방향은 전류 방향과 같으므로 전기 기호의 화살표 이미 터에서 베이스로 이동합니다. 순방향 바이어스에서 NPN 트랜지스터의 이미 터는 자유 전자를 방출하고 방향은 전류 방향과 반대이므로 전기 기호의 화살표는 베이스에서 이미 터로 이동합니다.

3.2.2 트랜지스터의 작동 원리

NPN 트랜지스터를 예로 들어보겠습니다. NPN 트랜지스터는 그림 11, a와 같이 두 개의 등가 다이오드(VD1 및 VD2)로 간주할 수 있습니다. VD1의 N-영역은 도핑 농도가 낮고 면적이 넓기 때문에 눈사태 고장이 잘 일어나지 않아 큰 역전압을 견딜 수 있다. 그러나 순방향 바이어스에서 VD1의 순방향 전류는 매우 작기 때문에 VD1은 역 차단 상태에서 작동하는 데 매우 적합합니다. VD1은 VD1이 역 상태에서 작동할 때 역포화 전류 ICBO를 생성하지만 N-영역과 P 영역의 도핑 농도가 매우 낮아 ICBO가 매우 작습니다. VD2의 N+ 영역은 도핑 농도가 높고 면적이 작기 때문에 눈사태 고장이 발생하기 쉬우므로 역내전압 능력이 매우 불량하다. 그러나 순방향 바이어스에서 VD1은 매우 큰 순방향 전류를 생성할 수 있으므로 VD2는 순방향 전도 상태에서 작동하는 데 매우 적합합니다. VD2가 순방향 상태에서 작동하면 두 개의 전류가 생성됩니다. 하나는 P 영역의 정공 흐름에 의해 생성된 전류 IEP이고 다른 하나는 N+ 영역의 전자 흐름에 의해 생성된 전류 IEN입니다. VD1의 P 영역의 도핑 농도는 N+ 영역의 도핑 농도보다 낮기 때문에 IEN은 IEP보다 크다. 이 두 등가 다이오드의 작동 원리를 알면 NPN 트랜지스터의 작동 원리를 쉽게 이해할 수 있습니다.

공통 이미 터 연결 방법을 통해 NPN 트랜지스터를 연결하십시오. 컬렉터 전원 공급 장치 EC와 컬렉터 저항 RC는 컬렉터와 이미 터에 직렬로 연결됩니다. 기본 전원 공급 장치 EB 및 기본 저항 RB는 기본 및 이미 터에 직렬로 연결됩니다. 이 회로에서 전류는 컬렉터와 베이스에서 NPN 트랜지스터로 흐르고 이미 터에서 NPN 트랜지스터 밖으로 흐릅니다. 컬렉터에서 흐르는 총 전류는 컬렉터 전류 IC입니다. 베이스에서 흐르는 총 전류는 베이스 전류 IB입니다. 이미 터에서 흐르는 총 전류는 이미 터 전류 IE입니다. IC와 IE 간의 선형 관계는 공통입니다. 기본 전류 이득 α이고 IC와 IB 간의 선형 관계는 공통 이미터 전류 이득 β. 도핑 농도의 차이로 인해 컬렉터 접합 J1는 순방향 바이어스에 적합하지 않고 이미터 접합 J2는 역방향 바이어스에 적합하지 않습니다. 편견. 컬렉터와 이미 터가 반대로 연결되면 NPN 트랜지스터 고장 가능성이 크게 높아집니다.

차단 상태: NPN의 구조는 항상 역 바이어스 상태에서 PN 접합을 만듭니다. 베이스에 전압이 인가되지 않은 경우 컬렉터와 에미터에 큰 전압(항복전압 BVCEO 미만)을 인가해도 NPN 트랜지스터가 켜지지 않습니다. 작은 누설 전류 ICEO).

활성 상태: NPN 트랜지스터를 켜려면 VD1과 VD2가 동시에 작동해야 하므로 J1 역방향 바이어스(UBC<0) 및 J2 순방향 바이어스(UBE>UTO)를 만들기 위해 베이스에 특정 전압을 인가해야 합니다. NPN 트랜지스터가 켜지면 내부 전류는 그림 11, b와 같이 등가 다이오드가 별도로 작동할 때와 약간 다릅니다. N+ 영역에서 P 영역으로 주입된 자유 전자는 P 영역의 정공과 완전히 재결합하지 않습니다. J2의 역 바이어스로 인해 자유 전자의 일부가 P 영역을 통과하여 N- 영역으로 직접 주입되어 역전류 ICN을 생성합니다. NPN 트랜지스터가 활성 상태에서 작동할 때 베이스 전류(IB)의 작은 변화는 콜렉터 전류(IC)의 큰 변화를 일으킬 것입니다. 이 현상을 컨덕턴스 변조 효과라고 합니다. 이 현상은 작은 입력 전류가 큰 출력 전류로 증폭되는 것과 같으므로 활성 상태를 증폭 상태라고도 합니다.

포화 상태: IB가 증가함에 따라 P 영역의 정공 농도가 감소하고 IEP가 감소하며 J1의 공핍 영역이 계속 증가합니다. 동시에 N+영역에서 P영역으로 주입되는 자유전자가 점점 줄어들기 때문에 IBN은 최소값 부근까지 떨어지며 IC에 대한 IB의 증폭효과가 약해지기 시작했다. IB와 IC가 더 이상 선형 관계를 갖지 않으면 NPN 트랜지스터가 포화 상태에 들어가기 시작합니다. 이때, IB가 증가할수록 IC가 서서히 증가하고 NPN 트랜지스터의 포화 깊이도 깊어지기 시작한다. N+ 영역의 거의 모든 자유 전자가 N- 영역에 주입되면 베이스 전위는 컬렉터 전위와 동일합니다(UBC=0). 이때 NPN 트랜지스터는 깊은 포화 상태에 있으며 IC는 IB의 영향을 전혀 받지 않습니다. J1의 공핍 영역이 증가함에 따라 J1에 대한 애벌랜치 브레이크다운 가능성도 증가한다는 점에 유의해야 합니다.

* 트랜지스터의 계산 공식

IC = ICN + ICBO, (1)

IB = IBN + IEP - ICBO, (2)

IE = IC + IB = ICN + IBN + IEP, (3)

IC > 0이므로 IE / IC = IB / I C + 1; (4)

α = ICN / IE = (IC - ICBO) / IE, (5)

β = ICN / (IB + ICBO) = (IC - ICBO ) / (IB + ICBO), (6)

왜냐하면 IC > IB >> ICEO >> ICBO ≈ 0, 모든 누출을 무시하는 경우 현재, 우리는 α ≈ IC / IE, β ≈ IC / IB, < 엠>(7)

그러면 1/α = 1/β + 1, (8)을 얻을 수 있습니다.

따라서 α와 β 사이의 관계는 α = β / (1 + β), β = α / (1 - α)입니다. (9)

* 누설 전류

컬렉터 접합 역포화 전류 ICBO와 침투 전류 ICEO는 모두 트랜지스터에서 피할 수 없는 누설 전류입니다. 트랜지스터의 이미터(IE=0)를 열고 컬렉터와 베이스에 전압을 인가하면 그림과 같이 ICBO 값을 측정할 수 있습니다. 12, 에이. 트랜지스터의 베이스(IB=0)를 열고 컬렉터와 이미터에 전압을 인가하면 그림과 같이 ICEO 값을 측정할 수 있습니다. 12, 나.

컬렉터 접합 역포화 전류 ICBO의 생성 메커니즘은 그림 11, a에 나와 있습니다.

침투 전류 ICEO의 생성 메커니즘은 다음과 같습니다. 외부 전기장의 작용에 따라 컬렉터 영역의 다수 캐리어가 PN 접합에서 멀어져 공간 전하 영역이 넓어집니다. 컬렉터 접합 J1의 내장 전기장이 강화되어 드리프트에 도움이 됩니다. 모션; 이미터 영역의 다수 캐리어가 PN 접합에 더 가깝게 이동하여 공간 전하 영역을 좁히고 이미터 접합 J2의 내장 전기장이 약화되어 드리프트 모션에 도움이 되지 않습니다. . 따라서 내장된 전기장의 작용하게 베이스 영역의 소수 캐리어는 J1을 통해 컬렉터 영역으로 드리프트 합니다. 동시에 컬렉터 영역의 소수 캐리어는 J1을 통해 베이스 영역으로 드리프트 하며, 일부는 베이스 영역의 재결합에 참여하고 다른 부분은 이미터 영역으로 확산됩니다. J2. 기본 영역의 낮은 도핑 농도로 인해 기본 영역의 재조합에 참여하는 소수 캐리어의 비율이 매우 낮습니다. 이 과정이 트랜지스터를 켤 때 IEN이 생성되는 메커니즘과 매우 유사하다는 것을 찾는 것은 어렵지 않습니다. 따라서 ICEO와 ICBO 사이에는 선형 관계가 있습니다. ICEO = (1 + β) * ICBO. 그러나 컬렉터 영역과 베이스 영역의 낮은 도핑 농도로 인해 ICEO의 값은 매우 낮고 일반적으로 무시할 수 있습니다. 실리콘 트랜지스터의 ICEO는 일반적으로 100nA 미만입니다. 게르마늄 트랜지스터의 ICEO는 일반적으로 100μA 미만입니다.

* 컨덕턴스 변조 효과

컨덕턴스(G)는 저항의 역수이며 단위는 지멘스(S)입니다. 전도도 변조 효과(베이스 영역 전도도 조절 효과 또는 웹스터 효과라고도 함)는 BPT(바이 폴라 트랜지스터)의 기본 특성 중 하나로, 베이스 영역의 전도율(또는 베이스 영역은 밤이 폴라 트랜지스터의 작동 전류가 클 때 크게 감소합니다. BJT를 제외하고 SCR, GTO, GTR과 같은 다른 밤이 폴라 트랜지스터와 IGBT의 기생 트랜지스터는 모두 전도도 변조 효과가 있습니다. 웹스터 효과 외에도 밤이 폴라 트랜지스터의 작동 전류가 클 때 얼리 효과(컬렉터 접합 전압의 변화가 베이스 영역의 폭의 변화로 이어지는 현상)와 커크 효과( 베이스 영역의 너비가 증가하는 현상)도 나타납니다.

3.3 트랜지스터의 주요 매개변수

1- 공통 기본 전류 이득 α

공통 베이스 전류 이득 α(전체 이름은 "하이브리드 매개변수 순방향 전류 이득, 공통 베이스", HFB)이며, 이미터 효율 계수와 베이스 영역 전송 계수, α = FE * FB에 의해 결정됩니다. 베이스가 제로 바이어스(UBC = 0)일 때 베이스 단락 증폭 계수 α0는 이미터 효율 계수, 베이스 영역 전송 계수에 의해 결정됩니다, 컬렉터 효율 계수 및 애벌랜치 곱셈 계수, α0 = FE * FB * FC * M.

에미터 효율 계수 FE는 베이스 영역에 주입된 전자 전류 IEN과 에미터 전류 IE의 비율이며, FE = IEN / IE = IEN / (IEN + IEP) = 1 / [1 + (IEP / IEN) ]입니다. 베이스 영역의 도핑 농도를 줄임으로써 베이스 영역의 총 불순물 양은 에미터 영역의 총 불순물 양보다 훨씬 적으므로 에미터에서 베이스 영역으로 주입되는 소수 캐리어의 수를 효과적으로 늘릴 수 있습니다. 지역. IEP 대 IEN의 비율이 0에 가까울수록 트랜지스터의 발광 효율이 높아집니다.

베이스 영역 수송 인자 FB는 베이스 영역에 주입된 전자 전류 IEN에 대한 컬렉터 영역에 도달하는 전자 전류 ICN의 비율, FB = ICN/IEN이다. 베이스 영역의 폭을 줄임으로써 에미터 영역의 캐리어가 베이스 영역에 머무르는 시간을 효과적으로 단축할 수 있으므로 베이스 영역을 통과하는 소수 캐리어의 수를 늘릴 수 있습니다. 베이스 영역의 폭이 작을수록 베이스 영역의 에미터 영역에서 전자의 재결합 손실이 작아집니다.

컬렉터 효율 계수 FC는 컬렉터 영역에 도달하는 전자 전류 ICN에 대한 컬렉터 전류 IC의 비율, FC=IC/ICN입니다.

애벌랜치 증배 인자 M은 컬렉터 접합의 역 전압이 애벌랜치 항복 전압에 가깝게 증가할 때 애벌랜치 증배 효과를 설명하는 데 사용됩니다. 일반적으로 다음 공식으로 추정됩니다. M = 1 / [1 - (V / VB) ^n], n은 PN 접합(실리콘: n=1.5- 4, 게르마늄: n=2.5-8); VB는 컬렉터 J1의 역 항복 전압입니다. V는 컬렉터 접합의 전압입니다. V의 절댓값이 VB의 절댓값으로 가는 경향이 있을 때, M은 무한대가 되는 경향이 있고 애벌랜치 브레이크 다운은 PN 접합에서 발생합니다.

일반적으로 hFB(α)는 공통 베이스 DC 전류 이득을 표현하는 데 사용되며, hFB(α) = IC / IE이며 그 범위는 일반적으로 0.95-0.99입니다. ; hfb(α)는 공통 베이스 AC 전류 이득을 표현하는 데 사용됩니다. hfb(α) = Δ IC / Δ IE. 일반적으로 hfb(α) ≈ hFB(α).

2- 공통 이미 터 전류 이득 β

공통 이미 터 전류 이득 β (전체 이름은 "하이브리드 매개 변수 순방향 전류 이득, 공통 이미 터", HFE)은 컬렉터 전류 대 기본 전류의 비율이며 그 값은 일반적으로 1보다 훨씬 큽니다. 일반적으로 hFE(β) 멀티 미트로 직접 측정할 수 있는 공통 이미 터 DC 전류 이득, hFE(β) = IC / IB를 표현하는 데 사용됩니다. hfe(β)는 공통 이미터 AC 전류 이득을 표현하는 데 사용됩니다. hfe(β) = Δ IC / Δ IB. 트랜지스터의 전류 증폭 계수(또는 순방향 전류 이득)는 일반적으로 공통 이미 터 전류 이득 β를 나타냅니다.

3- 공통 컬렉터 전류 이득 γ

공통 컬렉터 전류 이득 γ(전체 이름은 "하이브리드 매개변수 순방향 전류 이득, 공통 컬렉터", HFC임)은 베이스 전류에 대한 이미터 전류의 비율입니다. 일반적으로 hFE(γ)는 공통 컬렉터 DC 전류 이득을 표현하는 데 사용됩니다. hFC(γ) = IE / IB; hfc(γ)는 공통 컬렉터 AC 전류 이득을 표현하는 데 사용됩니다. hfc(γ) = Δ IE / Δ IB. 이 매개변수는 평상시에는 거의 사용되지 않습니다.

4- 임계 전압 UTO

임계 전압 UTO는 트랜지스터의 이미터 접합 전도를 유발하는 전압입니다.

5- 특성 주파수 fT

특성 주파수 fT는 이득 대역폭 곱이라고도 하며 β=1일 때 트랜지스터의 작동 주파수로 정의할 수 있습니다. 동작 주파수 f0와 고주파 전류 증폭 계수 β를 알면 특성 주파수 fT를 얻을 수 있습니다. fT=β* f0. 작동 주파수가 증가함에 따라 배율이 감소합니다. 트랜지스터의 작동 주파수가 특성 주파수(f0 = fT)와 같으면 트랜지스터는 전류 증폭 기능을 완전히 잃습니다. 트랜지스터의 작동 주파수가 특성 주파수(f0> fT)보다 크면 트랜지스터가 정상적으로 작동하지 않습니다.

6- 최대 작동 전압 UCEM

최대 작동 전압 UCEM은 트랜지스터의 정격 전압입니다. 최대 작동 전압 UCEM을 초과하면 트랜지스터가 고장 납니다.

7- 최대 컬렉터 허용 전류 ICM

최대 컬렉터 허용 전류 ICM은 트랜지스터의 정격 전류입니다. 일반적으로 전류 이득 β가 최댓값에서 절반으로 떨어질 때 해당하는 컬렉터 전류 IC를 ICM로 지정합니다. 사용의 안전성을 보장하기 위해 일반적으로 이중 여백을 남겨 둘 필요가 있습니다.

8- 최대 수집기 소산 전력 PCM

최대 컬렉터 손실 전력 PCM은 트랜지스터가 최고 작동 온도(보통 25°C)에서 최고 접합 온도에 도달하는 전력입니다. 트랜지스터가 최대 접합 온도에 도달하면 내부 PN 접합 구조가 영구적으로 파괴됩니다.

3.4 트랜지스터의 기본 특성

안정된 동작 동안의 트랜지스터의 파라미터들(이 파라미터들은 일반적으로 고정된 값이거나 천천히 변화함) 사이의 관계를 정적 특성이라고 합니다. 턴 온 과정과 턴 오프 과정에서 트랜지스터의 매개변수 사이의 관계(이 매개변수는 일반적으로 급격히 변화함)를 동적 특성이라고 합니다. 트랜지스터의 입력 신호에 DC 신호만 있는 경우를 DC 동작(또는 정적 동작)이라고 합니다. 트랜지스터의 입력 신호에 교류 신호가 있으면 교류 동작(또는 동적 동작)이라고 합니다.

NPN 트랜지스터(공통 이미 터 연결)의 경우 입력이 베이스이고 출력이 컬렉터이므로 입력 전류는 IB, 입력 전압은 UBE , 출력 전류는 IC(출력 회로의 저항 RC에서 출력), 출력 전압은 UCE입니다.

3.4.1 트랜지스터의 정적 특성

트랜지스터의 정적 특성은 입력 특성(입력 전류와 입력 전압의 관계), 출력 특성(출력 전류와 출력 전압의 관계), 온도(온도가 입력 특성 및 출력 특성에 미치는 영향) 및 안전 동작 영역으로 구분됩니다. (트랜지스터의 안정적인 작동 조건).

1- 입력 특성

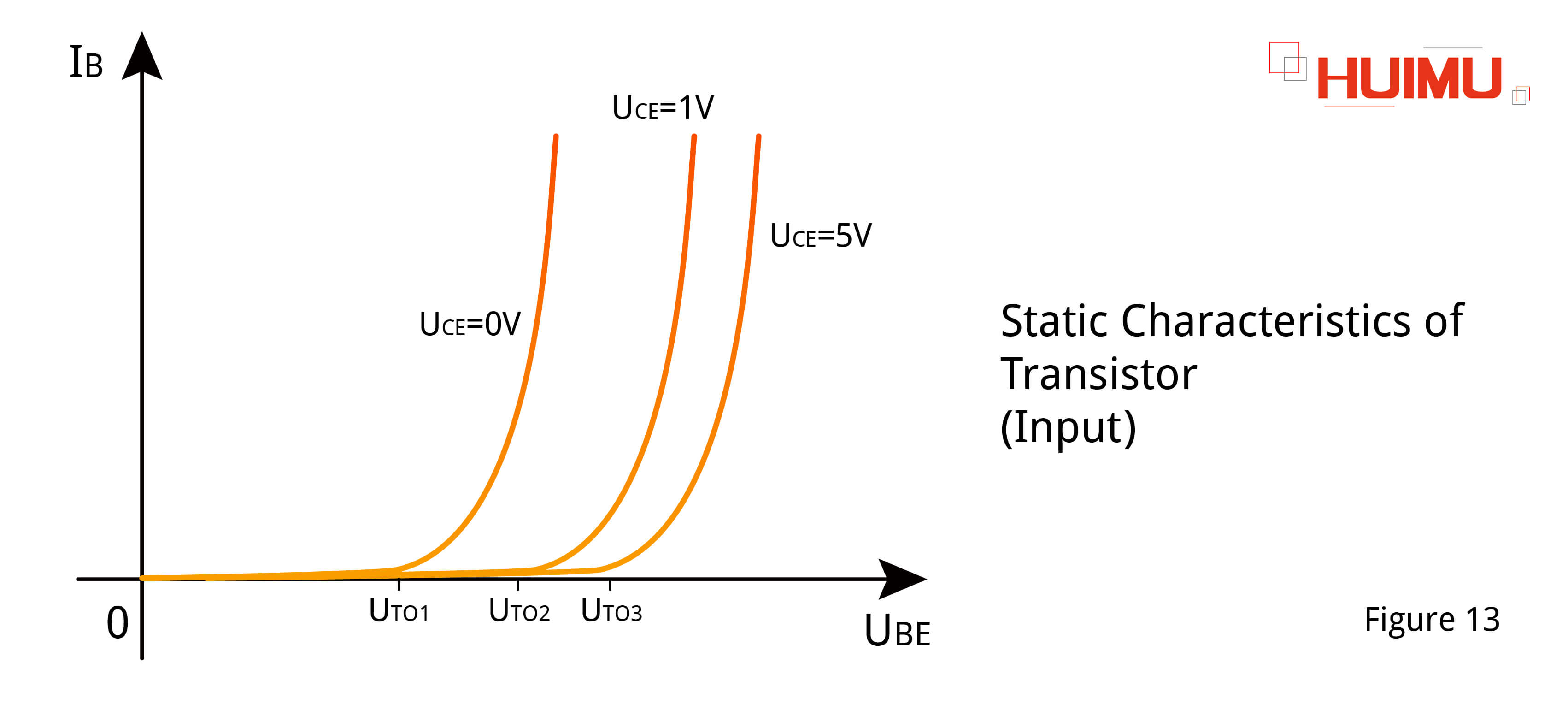

트랜지스터의 입력 특성은 그림과 같이 파워 다이오드의 순방향 입력 특성과 유사합니다. 13.

UCE가 고정 값이고 UBE>UTO일 때 기본 전류 IB는 다음과 같이 증가합니다. UBE 증가.

UCE가 증가하면 UTO가 증가하고 입력 특성 곡선이 오른쪽으로 이동합니다. UCE가 증가함에 따라 이미터 영역에서 베이스 영역으로 주입되어야 하는 캐리어의 일부가 베이스 영역을 통과하여 컬렉터 영역으로 직접 주입되기 때문에 캐리어가 베이스 영역의 농도가 너무 낮아 이미터 접합을 열 수 없습니다(즉, 이미터 접합의 확산 전류가 드리프트 전류보다 작거나 같음). 따라서 이미터 영역에서 베이스 영역으로 더 많은 캐리어를 주입하기 위해서는 UBE를 증가시킬 필요가 있으며(즉, 문턱 전압이 증가함), 입력 특성 곡선도 오른쪽으로 이동한다. UCE가 어느 정도 증가하면 이미터 영역에서 베이스 영역으로 주입될 수 있는 대부분의 캐리어가 컬렉터 영역으로 집결되므로 UCE 계속 증가하면 트랜지스터의 입력 특성을 거의 변경할 수 없습니다.

2- 출력 특성

트랜지스터의 출력 특성을 소개하기 전에 DC 부하 라인의 개념을 소개할 필요가 있습니다. DC 부하 라인은 트랜지스터가 정적 상태에서 작동할 때 콜렉터 부하 RC(출력 단자 저항)의 볼트-암페어 특성 곡선입니다. IC = (E< sub>C - UCE) / RC. 트랜지스터가 오프 상태가 되면 컬렉터 회로가 오프 상태가 되는 것과 같습니다. 이때 UCE=0, RC의 전압은 전원전압 EC와 같다. 트랜지스터가 온 상태에 들어갈 때 ICM은 출력 전류 IC의 가능한 최대값, 즉 RC를 통해 흐르는 최대 전류입니다. IC를 Y축으로, UCE를 X축으로 하여 직교좌표계에서 이 두 점을 표시하고 선분 즉, DC 부하를 그린다. 라인. DC 부하선과 Y축의 교차점을 포화점이라고 하고 X축과의 교차점을 차단점이라고 합니다. DC 부하선의 기울기는 RC의 저항값입니다.

DC 부하 라인과 트랜지스터의 출력 특성 곡선의 교차점을 정지 동작점 또는 Q 점이라고 합니다. 트랜지스터가 정적 작동점에서 작동할 때 입력 신호의 AC 신호가 어떻게 변하든 상관없이 트랜지스터는 안정적인 증폭 상태에서 작동하도록 보장할 수 있습니다(즉, 이미 터 접합은 순방향 바이 어스되고 컬렉터 접합은 역 바이어스) 비선형 왜곡이 발생하지 않습니다. Q 포인트를 선택할 때 최상의 증폭 효과를 얻으려면 트랜지스터의 포화 영역(포화 왜곡 방지)과 차단 영역(컷오프 왜곡 방지)에서 멀리 떨어져 있어야 합니다.

트랜지스터는 주로 컬렉터 접합 J1의 역전류를 통해 출력하므로 출력 특성 곡선은 파워 다이오드의 역 바이어스 하에서의 정적 특성 곡선(그림 14 참조). 파워 다이오드와 비교할 때 트랜지스터에는 세 가지 작동 상태가 있습니다. 출력 전류 IC와 입력 전류 IB의 관계를 직관적으로 이해하기 위해 X축을 왼쪽으로 확장하고 왼쪽 부분을 X축은 IB의 양의 X 반쪽 축으로 간주할 수 있습니다. Q 포인트는 IC 및 IB의 특성 곡선을 0, A, B 및 C의 4개 섹션으로 나누는 두 번째 사분면에 투영됩니다. 이 섹션은 해당 트랜지스터의 작업 영역으로

차단 영역(섹션 0): UBE≤ UTO 또는 IB=0일 때 이미 미터 접합은 꺼진 상태입니다. . 이때, 컬렉터 접합이 역 바이어스(UBC<0) 되어도 트랜지스터는 여전히 오프 상태(실제로는 매우 작은 침투 전류 ICEO). 마찬가지로 컬렉터 접합이 오프 상태(IC=0)인 경우 이미 터 접합이 순방향 바이어스(UBE>0) 되더라도 트랜지스터는 켜지지 않습니다. 따라서 트랜지스터의 차단 조건은 IC * IB = 0입니다.

활성 영역(섹션 A): 이미터 접합이 순방향 바이 어스되고 임계 전압보다 클 때(UBE>UTO>0), I B>0, 컬렉터 접합이 역 바이 어스되면(UBC≤0), 트랜지스터는 활성 영역(증폭 영역)에서 작동합니다. 이때 IC의 값은 UCE와는 아무런 관련이 없고 IB에만 영향을 받으며, IB와 IC 사이의 선형 관계, IC = β * IB.

채도 영역(섹션 B, 섹션 C): 베이스 전류가 증가함에 따라 베이스 영역의 정공 수가 감소하고, 이미터 영역에서 베이스 영역으로 주입되는 캐리어도 감소하여 베이스 영역의 공핍층이 넓어짐. 포화 경계에 도달하면 트랜지스터의 증폭 능력이 약해지기 시작합니다(β' = Δ IC / Δ IB < β), I B와 IC는 더 이상 선형 관계가 아니며 트랜지스터는 중포화 상태(얕은 포화 상태, 섹션 B)에 들어가기 시작합니다. 베이스 영역의 구멍수가 임곗값으로 떨어지면 베이스 영역의 전위는 컬렉터 영역의 전위와 동일합니다. 즉, 컬렉터 접합 J1는 0입니다. 바이어스(UBC=0)이고 베이스 전류는 증폭 효과를 완전히 잃습니다(β' = Δ IC / Δ IB = 0), 트랜지스터는 완전히 포화 상태(깊은 포화 상태, 섹션 C)에 들어갑니다.

트랜지스터가 얕게 포화되면 베이스 전류 IB가 작고 전도 전압 강하가 크며, 즉 트랜지스터의 등가 저항이 커서 포화 상태에서 빠져 나오기 쉽습니다. . 트랜지스터가 포화 상태일 때 베이스 전류 IB는 크고 전도 전압 강하는 작습니다. 즉, 트랜지스터의 등가 저항은 작습니다. 그리고 IB가 증가하면 트랜지스터의 포화 상태가 계속 심화되어 포화 상태를 벗어나기 어렵습니다. 실제 동작에서 IB(sat) = EC / (β * ICM)일 때, 트랜지스터는 일반적인 의미의 포화 상태인 깊은 포화 상태에 들어갔다. 때로는 트랜지스터를 깊은 포화 상태로 가속하기 위해 IB(sat)의 몇 배인 기본 전류가 인가됩니다. 트랜지스터의 작동 상태는 출력 저항 RC의 영향도 받는다는 점에 유의해야 합니다. 출력 저항 RC가 작을수록 포화 전류 IC가 커집니다. , 포화 전압 강하 UCE가 클수록 포화 트리거 전류 IB가 커집니다. 출력 저항 RC가 감소함에 따라 포화 전류 IC가 ICM에 접근하여 트랜지스터가 쉽게 연소됩니다. 출력 저항 RC가 0에 가까우면 트랜지스터가 소손되어도 포화 상태로 들어갈 수 없습니다. 따라서 출력 저항이 클수록 트랜지스터가 포화 상태에 들어갈 가능성이 더 높아집니다.

3- 온도

온도가 상승하면 반도체의 고유 열 여기가 발생하여 반도체 내부의 캐리어 농도가 증가합니다. 전도성을 증가시킵니다. 전도도의 증가는 누설전류의 증가, 문턱전압의 감소, 전류 이득의 증가 등의 원인이 됩니다. 따라서 트랜지스터의 입력 특성곡선은 온도가 상승함에 따라 우측으로 이동하고 출력특성곡선은 트랜지스터의 온도가 상승함에 따라 위로 이동합니다. 온도가 상승하면 트랜지스터의 열파괴 가능성도 높아지므로 실제 사용에서는 트랜지스터에 충분한 방열 조건을 갖추어야 합니다.

4- 안전한 작동 영역

트랜지스터의 모델이 알려진 경우 해당 PCM 매개변수도 알려져 있습니다. PCM=IC * UCE를 통해 PCM 곡선을 그릴 수 있습니다. ICM, UCEM, PCM 곡선은 트랜지스터의 SOA(안전 작동 영역)를 결정할 수 있습니다. 이 영역에서 트랜지스터 손상 없이 안정적으로 작동할 수 있습니다. 안전 작동 영역 밖의 영역은 위험 영역입니다. 위험 지역에서는 트랜지스터의 온도가 크게 증가하여 열 파괴에 더 취약합니다. 따라서 트랜지스터는 위험한 지역에서 작동하는 것을 피해야 합니다.

3.4.2 트랜지스터의 동적 특성

1- 켜기 프로세스

켜짐 조건(UBE> UTO)이 충족되면 트랜지스터가 켜집니다. 트랜지스터의 턴 온 과정은 지연 시간 td, 상승 시간 tr 및 확산 시간 ts로 구분됩니다. .

지연 시간 td는 10% IB1에서 10% IC1까지 걸리는 시간입니다. 이 시간은 배리어 커패시터를 충전하는 데 필요한 시간입니다.

상승 시간 tr은 IC가 10% IC1에서 90% IC1. 이 기간 동안 IC가 급격히 상승했습니다.

확산 시간 ts는 IC가 90% IC1에서 100% IC1. 이 시간은 확산 커패시터를 충전하는 데 필요한 시간입니다.

켜짐 시간의 계산 공식: ton=td + tr + ts

2- 종료 프로세스

차단 조건(IB=0)이 충족되면 트랜지스터가 꺼집니다. 트랜지스터의 턴 오프 과정은 저장 시간 ts, 하강 시간 tf 및 테일 시간 tt로 나뉩니다. .

저장 시간 ts는 90% IB1에서 90% IC1까지 걸리는 시간입니다. 이 기간은 포화 전도 동안 베이스 영역에 저장된 캐리어를 제거하는 데 필요한 시간입니다.

하강 시간 tf는 IC가 90% IC1에서 10% IC1. 이 기간 동안 IC가 급격히 떨어졌습니다.

테일 타임 tt는 IC가 10% IC1에서 ICEO로 떨어지는 데 걸리는 시간입니다. . 이 기간은 나머지 캐리어의 재조합에 필요한 시간입니다.

꺼짐 시간의 계산 공식: toff = ts + tf + tt

§4. 반 제어 장치 란 무엇입니까?

4.1 반 제어 장치 소개

반 제어 장치(사이리스터 또는 실리콘 제어 정류기 SCR이라고도 함)는 제어 신호(게이트 트리거)를 통해 켤 수 있지만 끌 수 없는 양극성 장치입니다. 사이리스터는 1956년에 탄생했으며 1960년대와 1970년대에 매우 광범위한 응용 분야를 가지고 있습니다. 그러나 1980년대 완전 제어 장치의 탄생과 함께 사이리스터의 위상은 점차적으로 대체되었습니다. 그러나 사이리스터는 매우 큰 전압과 전류를 견딜 수 있고 구조가 간단하고 작동이 안정적이기 때문에 대용량 애플리케이션에서 여전히 중요한 위치를 유지하고 있습니다. 사이리스터에는 3개의 단자가 있습니다. 사이리스터는 모양에 따라 볼트형(보통 볼트는 양극으로 라디에이터와 단단히 연결되고 설치가 용이함)과 플랫형(플랫 사이리스터는 두 개의 라디에이터로 고정될 수 있음)으로 나눌 수 있습니다. 게이트 트리가 링 외에도 사이리스터는 다음과 같은 이유로 켜집니다. 애노드 전압이 매우 높은 값으로 상승하고 애벌 런치 효과를 유발합니다. 양극 전압 상승률 dv/dt가 너무 높으며, 즉 PN 접합의 접합 커패시턴스 효과입니다. 접합 온도가 높습니다. 라이트 트리거. 전반적으로 게이트 트리가 링만이 가장 정확하고 신속하며 안정적인 제어 방법입니다. 그러나 반도체 기술의 발전으로 인해 이제 모듈식 사이리스터가 일반적입니다(더 보려면 클릭하세요. 사이리스터 모듈).

4.2 사이리스터는 어떻게 작동합니까?

4.2.1 사이리스터의 기본 구조

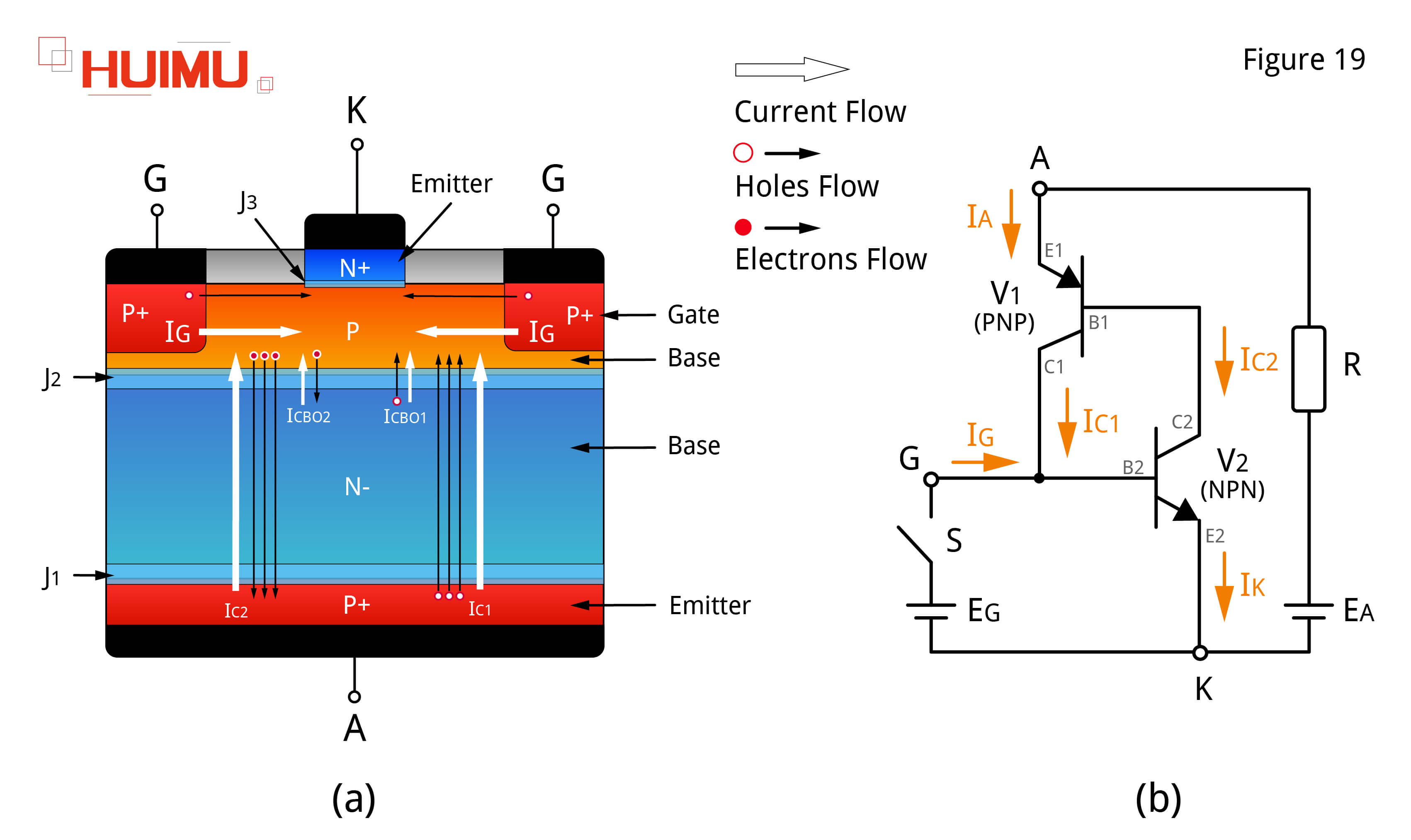

사이리스터는 트랜지스터보다 PN 접합이 하나 더 많은 P-N-P-N 4층 구조를 가지고 있습니다. 사이리스터는 양극 A, 음극 K, 게이트 G의 3개의 단자를 가지고 있습니다. 사이리스터의 P형 반도체와 N형 반도체의 도핑 정도는 다릅니다. 사이리스터의 내부 구조는 그림 19, a와 같이 두 개의 트랜지스터 V1 및 V2와 동일할 수 있습니다. V1은 PNP 트랜지스터(P+|N-|P)입니다. P+ 영역은 이미터 영역, N- 영역은 베이스 영역, P 영역은 컬렉터 영역입니다. V2는 NPN 트랜지스터(N+|P|N-)입니다. N+ 영역은 이미터 영역, P 영역은 베이스 영역, N- 영역은 컬렉터 영역입니다. 트랜지스터와 마찬가지로 사이리스터를 사용할 때 양극과 음극을 반대로 연결하여

4.2.2 사이리스터의 작동 원리

사이리스터의 등가 작동 회로는 그림 19, b에 나와 있습니다. V1 및 V2는 등가 트랜지스터입니다. 사이리스터의 양극과 음극은 출력 회로에 연결되고, 사이리스터의 게이트는 입력 회로에 연결됩니다. EA는 출력 회로의 전원이고 EG는 입력 회로의 전원입니다. R는 출력 저항입니다. IC1은 V1의 컬렉터 전류이고 IC2는 V2의 컬렉터 전류입니다. 애노드에 흐르는 전류는 애노드 전류 IA, 캐소드에 흐르는 전류는 캐소드 전류 IK, 게이트에 흐르는 전류는 게이트 전류 I< 하위>G. α1은 V1의 공통 기본 전류 이득이며, α2는 V2의 공통 베이스 전류 이득입니다. 사이리스터를 켜는 아이디어는 트랜지스터의 아이디어와 유사합니다. 즉, PN 접합 J2가 더 큰 역전류를 생성하도록 하는 방법입니다.

차단 상태: 순방향 바이어스 전압 UAK를 사이리스터의 음극과 양극에 인가하고 게이트에 전압을 가하지 않으면 컬렉터와 베이스 V1 및 V2는 열려 있고 사이리스터는 오프 상태입니다. 순방향 바이어스 전압의 영향으로 J1과 J3의 공핍층이 좁아지고 J2의 공핍층이 더 넓어지므로 J2에 역포화 전류 ICBO가 있습니다. -- 이 전류는 두 부분으로 구성되며, 하나는 정공 전류 ICBO1(V1) 의 공통 베이스 전류, 다른 하나는 자유 전자 전류 ICBO2(V2) 의 공통 베이스 전류 . 이 두 전류는 J1 및 J3을 통해 흐르고 두 등가 트랜지스터의 누설 전류 합보다 약간 큰 사이리스터의 누설 전류를 형성합니다. . 긍정적인 차단 상태에서 α1 + α2는 매우 작습니다.

전도 상태: 순방향 바이어스가 사이리스터의 게이트에 적용될 때 P+ 영역은 P 베이스 영역에 많은 수의 정공을 주입합니다. 그 중 일부는 N+ 영역으로 들어가 J3를 만듭니다. 순방향 전도 및 많은 수의 자유 전자가 N + 영역에서 P 염기 영역으로 주입되고 P 염기 영역의 소수 캐리어 농도가 증가하여 ICBO2가 증가합니다. 그것의 다른 부분은 N-영역으로 들어가고 N-영역의 소수 캐리어 농도를 증가시키므로 ICBO1가 증가합니다. 이러한 누설 전류는 모두 N 영역의 소수 캐리어를 줄이고 J1의 공핍층을 좁힙니다. J1의 공핍층을 어느 정도 좁힐 정도로 충분히 큰 게이트 순방향 바이어스를 가하면 J1의 동적 균형이 깨지고 많은 수가 P+영역에서 N-영역으로 정공이 주입되어 역전류의 형태로 P영역으로 흘러들어와 전류 IC1를 형성한 후 사이리스터 외부로 흐른다. 순방향 전류 형태의 N+ 영역; 유사하게, N+ 영역의 자유 전자는 P 영역에서 P+ 영역으로 흐르고 전류 IC2를 형성합니다. IC1 및 IC2가 설정되지 않은 경우 기본 전도도가 매우 작아서 α1 + α2는 매우 작습니다. 그러나 IC1 및 IC2가 설정되면 컨덕턴스 변조 효과로 인해 , V1 및 V2 베이스 영역의 전도도가 증가하여 IC1 및 I C2. 이 두 전류 사이의 양의 피드백은 α1 + α2를 급격히 증가시키고 1에 접근하여 온 상태 전압 강하를 급격히 낮추고 양극 전류 IA가 급격히 상승하고 마침내 사이리스터를 켭니다.

* 사이리스터의 계산식

IC1 = α1 * IA + ICBO1, (10)

IC2 = α2 * IK + ICBO2, (11)

IK = IA + IG, (12)

IA = IC1 + IC2, (13)

IA = (α2 * IG + ICBO1 + ICBO2 ) /[1 - (α1 + α2) ]. (14)

공식 14에서 볼 수 있습니다.

α1+α2가 0에 접근하면 IA는 전류가 누출되는 경향이 있습니다.

α1+α2가 1에 접근하면 IA는 무한대가 되는 경향이 있습니다.

4.3 사이리스터의 주요 매개변수

4.3.1 정적 매개변수(전압)

1- 순방향 이 반복 피크 전압 UDSM / 역방향 이 반복 피크 전압 URSM

게이트가 열리면 순방향 이 반복 피크 전압 UDSM(최대 오프 상태 과도 전압이라고도 함)은 순방향의 급격한 굽힘 지점에 의해 결정되는 오프 상태 피크 전압입니다. 볼트-암페어 특성 곡선; 역방향 이 반복 피크 전압 URSM(최대 역 과도 전압이라고도 함)은 역 전압-암페어 특성 곡선의 급격한 굽힘 점에 의해 결정되는 오프 상태 피크 전압입니다.

2- 순방향 회전 전압 UBO

순방향 회전 전압 UBO는 양극과 음극 사이에 순방향 사인 반파 전압이 인가될 때 사이리스터가 오프 상태에서 온 상태로 천이하는 피크 전압을 나타냅니다. 사이리스터와 게이트는 정격 접합 온도(100℃)에서 개방된다.

3- 역 항복 전압 UBR

역방향 항복 전압 UBR는 역 사인 반파 전압이 사이리스터의 양극과 음극 사이에 인가될 때 사이리스터의 역 누설 전류를 급격히 증가시키는 피크 전압을 나타냅니다. 정격 접합 온도(100℃).

4- 순방향 오프 상태 반복 피크 전압 UDRM / 역 오프 상태 반복 피크 전압 URRM

순방향 오프 상태 반복 피크 전압 UDRM(오프 상태 반복 피크 전압이라고도 함)은 게이트가 열려 있고 접합이 닫힐 때 장치에 반복적으로 인가할 수 있는 순방향 피크 전압입니다. 온도가 평가됩니다. 반복률은 초당 50회이며, 각 시간의 지속시간은 10ms 이하이다. 일반적으로 UDRM은 UDSM의 90%로 지정됩니다. 그리고 UDRM은 UBO보다 100V 작아야 합니다.

역 오프 상태 반복 피크 전압 URRM(역 반복 피크 전압이라고도 함)은 게이트가 열려 있고 접합 온도가 평가했다. 반복률은 초당 50회이며, 각 시간의 지속시간은 10ms 이하이다. 일반적으로 URRM은 URSM의 90%로 지정됩니다. URRM 전압은 UBR보다 낮아야 합니다.

UDRM 및 URRM은 온도가 증가함에 따라 감소합니다. 테스트 및 사용 중에는 온도를 엄격하게 조절해야 합니다. 일반적으로 사이리스터의 정격 전압은 UDRM과 URRM 중 작은 쪽을 취합니다.

5- 게이트 트리거 전압 UGT

게이트 트리거 전압 UGT는 양극과 음극 사이에 일정 값의 순방향 전압이 인가될 때 사이리스터를 오프 상태에서 온 상태로 전환하는 데 필요한 최소 게이트 DC 전압을 나타냅니다. 지정된 주변 온도에서 사이리스터. UGT는 일반적으로 약 1.5V입니다.

6- 순방향 평균 전압 강하 UF

순방향 평균 전압 강하 UF(온 상태 평균 전압 또는 온 상태 전압 강화라고도 함)는 사이리스터의 온 상태 전류는 지정된 주변 온도 및 표준 방열 조건에서 정격 전류입니다. UF는 일반적으로 0.4-1.2V입니다.

7- 온 상태 피크 전압 UT

온 상태 피크 전압 UT는 사이리스터의 온 상태 전류가 정격 전류의 지정된 배수일 때 과도 피크 전압을 나타냅니다.

4.3.2 정적 매개변수(현재)

1- 정격 온 상태 전류 IT

정격 온 전류 IT는 지정된 주변 온도(40°C) 및 지정된 냉각 조건에서 사이리스터를 통해 흐를 수 있는 최대 전력 주파수 사인 반파 전류 값을 나타냅니다. 조건, 전도 각도가 170° 이상일 때, 부하는 저항성이고 안정적인 접합 온도가 정격 접합 온도를 초과하지 않습니다. 단방향 사이리스터는 정격 온 상태 평균 전류 IT(AV)를 정격 전류로 사용합니다. 양방향 사이리스터는 정격 온 상태 유효 전류 IT(RMS)를 정격 전류로 사용합니다. 전류 파형이 전력 주파수 사인 반파가 아닌 경우 사이리스터는 저항과 동일한 volt-ampere 특성 곡선이 없는 반도체이지만 동일한 유효값(동일한 발열 효과)을 갖는 저항을 기준으로 사용할 수 있습니다. 사이리스터의 정격 전류를 결정합니다(저항의 등가 계산 결과의 1.5-2배).

2- 오프 상태 누설 전류 IDRM / 역 누설 전류 IRRM

IDRM 및 IRRM은 각각 UDRM 및 URRM의 해당 누설 전류이며 일반적으로 100μ A 미만입니다. .

3- 게이트 트리거 전류 IGT

게이트 트리거 전류 IGT는 양극과 음극 사이에 일정 값의 순방향 전압이 인가될 때 사이리스터를 오프 상태에서 온 상태로 전환하는 데 필요한 최소 게이트 DC 전류를 나타냅니다. 지정된 주변 온도에서 사이리스터. 일반 사이리스터의 IGT는 일반적으로 몇 밀리암페어입니다. 고감도 사이리스터의 IGT는 일반적으로 수 마이크로 암페어입니다.

4- 유지 전류 IH

유지 전류 IH는 사이리스터를 전도 상태로 유지하는 데 필요한 최소 전류입니다. IH는 일반적으로 수십에서 수백 밀리암페어입니다. 게이트가 트리거되면 게이트 신호가 제거되어도 사이리스터는 여전히 켜져 있고, 사이리스터는 애노드 전류를 줄여야만 꺼질 수 있다. 양극 전류가 IH보다 작으면 사이리스터가 꺼집니다. 접합 온도가 높을수록 IH가 작을수록 사이리스터가 꺼질 가능성이 줄어듭니다.

5- 래핑 전류 IL

래핑 전류 IL은 사이리스터가 오프 상태에서 온 상태로 막 전환되고 게이트 신호가 제거된 후 사이리스터를 켜진 상태로 유지하는 데 필요한 최소 전류를 나타냅니다. 동일한 사이리스터의 경우 IL은 일반적으로 IH의 약 2-4배입니다.

6- 돌입 전류 ITSM

돌입 전류 ITSM은 전원 주파수 사인파의 반주기 동안 비정상적인 회로로 인한 사이리스터의 접합 온도가 정격 접합 온도를 초과할 때 이 반복적인 최대 순방향 과부하 전류를 나타냅니다. 일반적으로 순방향 파동에서 사이리스터는 정격 전류의 6배인 과부하 전류를 견딜 수 있습니다. 사이리스터의 수명 동안 서지 횟수의 제한을 초과하면 사이리스터가 영구적으로 손상될 수 있습니다.

7- 정희 전 전류 IBO

순방향 전류 IBO는 정격 접합 온도(100℃)에서 Gate가 개방되었을 때 사이리스터를 오프 상태에서 온 상태로 변화시킬 수 있는 피크 전류를 의미합니다.

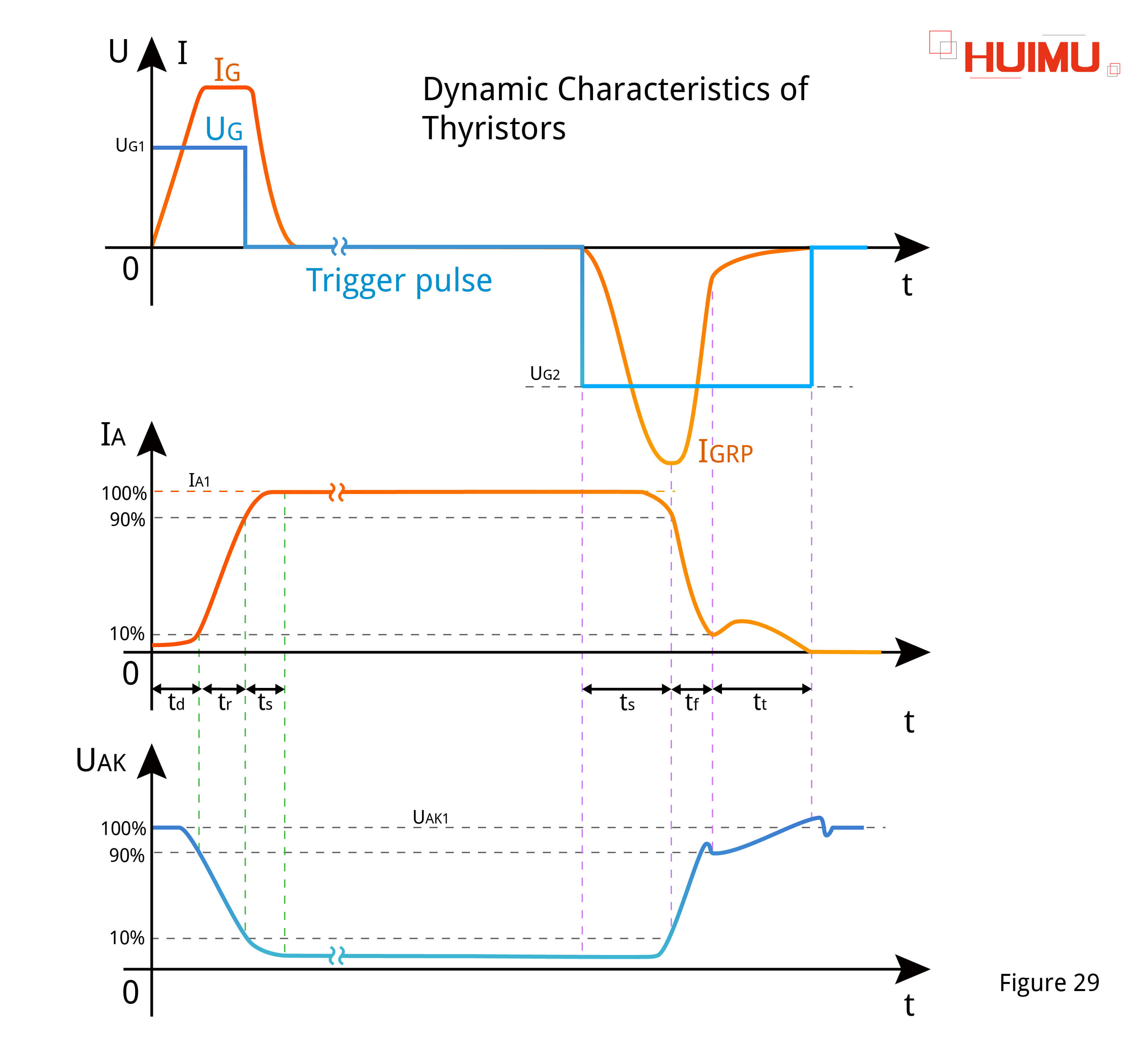

4.3.3 동적 매개변수

1- 켜짐 시간 tgt

턴 온 시간 tgt는 충분한 트리거 신호가 인가되었을 때 사이리스터가 오프 상태에서 온 상태로 전환되는 지연 시간을 나타냅니다. 턴 온 프로세스 동안 사이리스터의 출력 전압 UAK는 온 상태 전압 강하 UF 및 양극 전류 I로 점차 감소합니다. A는 정격 온 상태 전류 IT로 점차 증가합니다.

2- 꺼짐 시간 tq

꺼짐 시간 tq는 사이리스터의 켜짐 전류가 0으로 떨어질 때부터 사이리스터가 지정된 꺼짐 전압을 견디기 시작할 때까지의 시간 간격을 나타냅니다. 일반 사이리스터의 tq는 약 수백 밀리초입니다. tq는 튜브의 내부 구조와 관련이 있을 뿐만 아니라 온도, dv/dt, di/dt 등과도 관련이 있습니다. tq는 일반적으로 역 전압을 증가시켜 감소합니다. tq 동안 애노드 전압을 다시 인가하면 사이리스터를 다시 켤 수 있지만, tq가 지나면 어떤 방법을 사용해도 사이리스터가 꺼집니다. 양극 전압을 높이려면(사이리스터가 고장 나지 않은 경우).

tgt 및 tq는 사이리스터의 작동 주파수를 결정합니다. 높은 작동 주파수 회로의 경우 tq가 작은 사이리스터를 선택해야 합니다(tq가 작으면 tgt가 더 작음). . 이 매개변수는 일반 사이리스터와 고속 사이리스터의 주요 차이점입니다.

3- 임계 오프 상태 전압 상승률 dv/dt

임계 오프 상태 전압 상승률 dv/dt는 게이트가 정격 접합 온도에서 개방될 때 오프 상태에서 온 상태로 전환되는 사이리스터의 인가전압의 최대 상승률을 나타냅니다. 접합 커패시터 충전 전류가 클 때 전압 상승률이 너무 크면 충전 전류가 커져 사이리스터가 실수로 켜질 수 있습니다. 소전류 사이리스터(50-100A)의 dv/dt는 일반적으로 225V/μ s이고 대전류 사이리스터(200A 이상)의 dv/dt는 일반적으로 50V/μ s보다 큽니다.

4- 임계 온 상태 전류 상승률 di/dt

임계 온 전류 상승률 di/dt는 정격 접합 온도에서 게이트가 닫힐 때 사이리스터가 손상 없이 견딜 수 있는 온 전류의 최대 상승률을 나타냅니다. 사이리스터는 전원을 켤 때 큰 전력 손실을 발생시키며 제한된 전도 팽창 속도 때문에 이 손실은 항상 게이트 근처의 음극 영역에 집중됩니다. 전류가 너무 빨리 상승하면 전도 전류가 크지 않더라도 쉽게 사이리스터가 국부적으로 과열되어 게이트가 영구적으로 손상되고 사이리스터가 소손될 수 있습니다. 사이리스터의 정격 전류가 클수록 이 문제가 더 두드러집니다.

4.4 사이리스터의 기본 특성

4.4.1 사이리스터의 정적 특성

사이리스터의 정적 특성은 그림 20과 같이 출력 전류와 출력 전압의 볼트-암페어 특성입니다. UAK는 사이리스터의 양극과 음극에 인가되는 전압, I A는 양극 전류이고 IG는 트리거 전류입니다.

1- 순방향 정적 특성

정방향 차단 상태: IG = 0일 때 UAK> 0이면 작은 순방향 누설 전류만 있습니다. α1 + α2 도 매우 작습니다. 이때 사이리스터는 순방향 차단 상태이다. 그러나 UAK ≥ UBO 또는 IA ≥ IBO, α1 + α2가 1에 접근하고 사이리스터는 순방향 전도 상태로 들어갑니다.

순방향 전도 상태: 일반적인 순방향 전도 상황은 IG> 0, UAK ≥ UGT일 때 사이리스터 기본 영역의 전도도가 크게 증가합니다. α1 + α2가 1에 접근하면 사이리스터를 통해 흐르는 전류 IA가 무한대에 접근하고(IA의 실제 값은 외부 회로에 의해 결정됨) 마지막으로 포화 전도는 다음과 같습니다. 달성. 동일한 외부 조건에서 IG가 클수록 UGT가 작아집니다. 사이리스터가 켜지면 게이트가 제어 기능을 잃는다는 점에 유의해야 합니다. 사이리스터의 출력 전류 IA가 0에 가까운 특정 값으로 감소되어야만 사이리스터를 끌 수 있습니다.

2- 역 정적 특성

사이리스터의 역 정적 특성은 파워 다이오드의 역 정적 특성과 유사합니다. 사이리스터에 역전압이 가해지면 게이트에 트리거 전류가 있든 없든 간에 사이리스터는 켜지지 않고 아주 작은 역 누설 전류만 있습니다. 이때 사이리스터는 역 차단 상태이다. 그러나 역 전압이 역 항복 전압 UBR에 도달하면 사이리스터 눈사태 고장.

4.4.2 사이리스터의 동적 특성

1- 켜기 프로세스

사이리스터의 출력 단자에 UAK1을 인가하면 이때 사이리스터는 오프 상태가 되며 UAK는 100% UAK1. UG ≥ UGT 일 때 사이리스터가 전도 상태에 들어가기까지 시간이 걸립니다. 사이리스터가 켜지면 출력 단자 전압 UAK는 매우 작은 값, 즉 온 상태 전압 강하를 유지합니다.

사이리스터의 턴 온 과정은 지연 시간 td, 상승 시간 tr 및 확산 시간 ts로 구분됩니다. .

지연 시간 td는 IA가 순방향 누설 전류에서 10% IA1로 상승하는 데 필요한 시간이며 UAK: 100% UAK1에서 90% UAK1로 감소합니다. 지연 시간은 일반적으로 0.5-1.5μ s입니다. 게이트 전류가 증가함에 따라 지연 시간이 감소합니다.

상승 시간 tr은 IA가 10% IA1에서 90% IA1 및 UAK가 90% UAK1에서 10% UAK1로 감소합니다. 상승 시간은 사이리스터 자체의 특성, 외부 회로의 임피던스, 온도, 양극 전압 등에 영향을 받습니다. 상승 시간은 일반적으로 0.5~3μ s입니다. IA를 증가시키면 지연 시간 td와 상승 시간 tr을 크게 줄일 수 있습니다.

확산 시간 ts는 IA가 90% IA1에서 100% IA1 및 UAK를 사용하여 10% UAK1에서 온 상태 전압 강하로 떨어뜨립니다. 확산 시간은 음극의 단면적에 따라 다릅니다.

일반적으로 IA가 90% IA1에 도달하면 사이리스터가 켜진 것으로 간주할 수 있습니다. 따라서 켜짐 시간을 계산하는 공식은 다음과 같습니다. tgt = td + tr.

2- 종료 프로세스

UAK를 0으로 줄이거나 충분히 큰 역전압 UAK2를 적용하면 IA가 점차 감소하고 사이리스터는 온 상태에서 오프 상태로. 사이리스터의 턴 오프 과정은 역 차단 회복 시간 trr과 순차 차단 회복 시간 tgr로 구분된다.

턴 오프 과정에서 외부 회로의 인덕턴스로 인해 역 회복 전류 IR가 사이리스터에 나타납니다. IR이 점차 피크 값 IRP에 도달하면 해당 URP가 생성되고 IR은(는) 빠르게 소멸됩니다. IA가 0으로 떨어지는 시간부터 IR이 사이리스터의 역 누설 전류까지 떨어지는 시간을 역 차단 회복 시간 trr라고 합니다.

역 회복 과정이 끝난 후 사이리스터의 순방향 차단 능력이 완전히 회복될 때까지의 시간을 순방향 차단 회복 시간 tgr(또는 게이트 회복 시간)이라고 한다. tgr 동안 게이트 근처의 PN 접합에 소수의 캐리어가 남아 있기 때문에 여전히 사이리스터 내부의 포지티브 피드백 메커니즘을 트리거 할 수 있습니다. 사이리스터에 순방향 전압을 인가하면 사이리스터는 다시 순방향으로 도통합니다. 이 켜기 프로세스 중에는 게이트 트리거 신호가 필요하지 않습니다.

종료 시간 tq의 계산 공식은 다음과 같습니다. tq = trr + tgr.

4.5 사이리스터의 직렬 및 병렬연결

1- 사이리스터의 직렬연결

여러 사이리스터를 직렬로 연결하면 전체 전압 용량을 늘릴 수 있습니다. 실제로 사이리스터의 내전압 값에 숫자를 곱하여 전체 내전압 값을 얻는 것은 불가능합니다. 대신 각 사이리스터가 실제로 부담하는 전압에 의해 추가되어야 합니다. 이는 주로 각 사이리스터에 분포된 전압이 균일하지 않기 때문입니다(정적 불균일 전압과 동적 불균일 전압으로 구분).

Static Uneven Voltage: 직렬연결된 사이리스터를 통해 흐르는 누설 전류는 동일하지만 정적 볼트-암페어 특성이 분산되어 있기 때문에 각 사이리스터에 할당되는 전압이 동일하지 않습니다. 극단적인 경우 특정 사이리스터는 모든 전압을 견딜 수 있지만 다른 사이리스터는 매우 작은 전압 만 견딜 수 있습니다. 매우 유사한 매개변수 및 특성을 가진 사이리스터를 선택하여 정적 불균일 전압을 줄일 수 있습니다. 저항 균등화 방법은 정적 불균일성을 줄이기 위해 사용할 수도 있습니다. 즉, 사이리스터는 고 저항 저항(약 1메그옴)으로 간주되며 각 사이리스터는 등가 저항을 조정하기 위해 저 저항 저항과 병렬로 연결됩니다 각 병렬 회로의 등가 저항값이 매우 가까울 때 각 사이리스터에 분포된 전압도 매우 가깝습니다.

동적 불균일 전압: 동적 불균일 전압은 사이리스터의 동적 매개변수 및 동적 특성의 차이로 인해 발생합니다. 동적 매개변수와 특성이 가능한 한 일관된 사이리스터를 선택하면 동적 불균일 전압을 줄일 수 있습니다. 또한 강력한 게이트 펄스에 의해 트리거 되어 사이리스터의 켜짐 시간 차이를 크게 줄일 수 있습니다. 동적 전압 균등화를 위해 RC 병렬 분기를 사용할 수도 있습니다. 즉, RC 회로를 통해 과전압을 흡수하여 동적 조건에서 각 사이리스터가 견디는 전압이 매우 가깝도록 합니다.

2- 사이리스터의 병렬연결

여러 사이리스터를 병렬로 연결하면 전체 전류 용량을 늘릴 수 있습니다. 각 사이리스터의 매개변수와 특성이 다르기 때문에 불균일한 전류 분포도 고려해야 합니다. 동적 불균일 전류와 정적 불균일 전류를 줄이기 위해 가능한 한 일관된 특성과 매개 변수를 가진 사이리스터를 선택합니다. 전류 공유 리액터에 의해 동적 불균일 전류를 줄이는 것도 가능합니다(손실이 저항보다 작음). 또한 강력한 게이트 펄스 트리가 링을 사용하여 사이리스터의 턴 온 시간 차이를 크게 줄여 각 사이리스터가 짧은 시간에 효과적으로 트리거 되어 동적 전류 공유의 목적을 달성할 수 있습니다. 그러나 사이리스터의 전류 용량이 점점 커지고 있기 때문에 일반적으로 사이리스터를 병렬로 작동할 필요가 없습니다.

3- 사이리스터의 직렬 및 병렬연결

사이리스터를 직렬 및 병렬로 동시에 연결해야 하는 경우 일반적으로 각 사이리스터의 매개변수와 특성이 가능한 한 일관성을 유지하도록 먼저 직렬로 연결하고 두 번째로 병렬로 연결하는 것이 좋습니다.

4.6 사이리스터의 주요 유형

1- 빠른 스위칭 사이리스터

고속 스위칭 사이리스터(FST)는 우수한 동적 특성을 가지고 있습니다. FST는 일반 사이리스터에 비해 턴 온 시간이 짧고(일반적으로 4-8μ s), 턴 오프 시간이 짧으며(일반적으로 10-60μ s) dv/dt 및 di/dt의 허용 오차가 크다는 장점이 있습니다. 일반 사이리스터는 50Hz의 전압에서만 작동할 수 있는 반면 FST는 더 높은 주파수(400Hz 이상)의 회로에서 작동할 수 있습니다. 고주파 사이리스터(HFT)는 FST보다 스위칭 시간이 짧고 스위칭 속도가 빠르며 고주파 회로(10kHz 이상) 작업에 적합합니다. 높은 작동 주파수로 인해 FST 및 HFT의 스위칭 손실 가열 효과를 무시할 수 없으므로 정격 전압 및 정격 전류는 일반적으로 높지 않습니다.

2- 양방향 3극관 사이리스터

양방향 사이리스터(양방향 3극관 사이리스터, 3극관 AC 스위치, TRIAC라고도 함)는 한 쌍의 역병렬 연결 단방향 사이리스터(SCR)로 간주할 수 있습니다. 양방향 사이리스터는 AC 솔리드스테이트 릴레이 및 모듈의 공통 핵심 장치입니다(더 많은 AC 무접점 릴레이를 보려면 클릭하세요). 양방향 사이리스터의 순방향 특성은 단방향 사이리스터의 특성과 동일하지만 역방향 특성은 단방향 사이리스터의 특성과 다릅니다. 양방향 사이리스터에는 역 차단 기능이 없습니다. 양방향 사이리스터의 특성곡선이 중심대칭임을 좌표 축에서 명확히 알 수 있다. 양방향 사이리스터는 T1 극(P형 반도체 물질에 연결된 주전급), T2극(N형 반도체 물질에 연결된 주전급) 및 게이트 G 극을 갖는다. 양방향 사이리스터의 정격 전류는 정격 온 상태 유효 전류 IT(RMS)입니다. 양방향 사이리스터의 매개변수에는 순방향 피크 전압과 역방향 피크 전압이 없고 최대 피크 전압만 있습니다. 양방향 사이리스터의 다른 매개변수는 단방향 사이리스터와 동일합니다.

3- 역전도 사이리스터

RCT(역전도 사이리스터)의 설계 아이디어는 양방향 사이리스터와 유사하지만 역전도 사이리스터는 역병렬 연결을 위해 전력 다이오드를 사용하므로 양극과 음극의 이미터 접합이 모두 단락 상태. 이 특별한 구조로 인해 역전도 사이리스터는 낮은 온 상태 전압, 짧은 턴 오프 시간, 높은 정격 접합 온도, 높은 전압 저항, 높은 온도 저항 등의 장점이 있습니다. 예를 들어 턴 오프 시간 역전도 사이리스터의 (수 마이크로초) 및 전력 주파수(수십 kHz)는 고속 스위치 사이리스터의 것보다 분명히 우수합니다. 역전도 사이리스터는 사이리스터와 프리 휠링 파워 다이오드의 유기적 조합으로 간주할 수 있어 회로 설계를 단순화할 수 있으며 스위칭 전원 공급 장치 및 UPS와 같은 애플리케이션에 널리 사용됩니다.

4- 라이트 트리거 사이리스터

광 트리거 사이리스터(LTT 또는 광 제어 사이리스터라고도 함)는 게이트 영역이 광전 전력 다이오드를 통합하고 광 신호의 강도를 사용하여 게이트 트리거 전류를 대체하는 사이리스터입니다. 따라서 라이트 트리거는 일종의 게이트 트리거입니다. 광 제어 사이리스터의 트리거 감도를 향상시키기 위해 게이트 영역은 종종 증폭 게이트 구조 또는 이중 증폭 게이트 구조를 채택합니다. 라이트 트리거는 주 회로와 제어 회로 사이의 전기 절연을 보장하고 전자기 간섭의 영향을 피할 수 있습니다. 저전력 광 제어 사이리스터는 고 전력 사이리스터에 대한 트리거 신호를 제공하기 위해 전기 절연에 자주 사용됩니다. 고출력 광 제어 사이리스터는 제어 회로와 주 회로 사이의 절연을 양호하게 할 수 있으며 고전압 전력 장비(예: 고전압 직류 전송)에 사용됩니다.

§5. 완전 제어 장치 란 무엇입니까?

5.1 완전 제어 장치 소개

완전 제어 장치(자체 차단 장치라고도 함)는 제어 신호에 의해 켜지고 꺼지도록 제어할 수 있는 장치입니다. 1980년대 완전 제어 장치의 탄생 이후 전력 전자 기술은 새로운 시대로 접어들었습니다. 완전히 제어되는 많은 유형의 장치가 있으며 대부분은 다양한 분야의 요구를 충족할 수 있는 고유한 특성을 가진 복합 구조를 사용합니다. 완전 제어 장치에는 주로 게이트 오프 사이리스터(GTO), 밤이 폴라 접합 트랜지스터(GTR 등 포함), 전계 효과 트랜지스터 EFT(MOSFET, JFET 등 포함) 및 복합 장치(IGBT, MCT, SIT, SITH, IGCT 등). 다음 내용은 그들에 대한 간략한 소개를 제공할 것입니다.

5.2 게이트 차단 사이리스터

5.2.1 GTO 소개

게이트 턴 오프 사이리스터(GTO)는 사이리스터의 등장 직후 등장한 사이리스터의 파생 소자이다. 일반 사이리스터(SCR)는 반 제어 장치이며 SCR이 켜진 후에는 게이트 신호가 더 이상 영향을 미치지 않습니다. GTO는 게이트에 음의 펄스 신호를 적용하여 끌 수 있는 완전히 제어되는 장치입니다.

5.2.2 GTO는 어떻게 작동합니까?

5.2.2.1 GTO의 기본 구조

GTO의 구조는 SCR과 유사하지만 GTO는 N+ 버퍼 영역이 하나 더 있으므로 GTO의 턴 온 시간은 SCR보다 짧지만 동시에 역 차단 능력은 SCR보다 약합니다. GTO는 공통 양극을 가진 수십 또는 수백 개의 GTO 장치로 구성된 다중 장치 전원 통합 장치입니다. 이 GTO 장치의 음극과 게이트는 장치 내부에서 병렬로 연결됩니다. 이 집적 구조에서 각 GTO 유닛의 음극 영역은 작고 게이트와 음극 사이의 거리가 크게 단축되어 P2 베이스 영역의 측면 저항이 작아지고 게이트에서 더 큰 전류를 끌어올 수 있으므로 V1의 컬렉터는 차단되기 쉽고 최종적으로 사이리스터를 끄기 쉽게 만듭니다. 이 통합 구조는 또한 GTO의 켜짐 속도를 SCR보다 빠르게 만들고 di/dt 베어링 용량과 과부하 베어링 용량이 더 강합니다. 국부적 과부하 및 과열로 인한 손상; GTO의 모든 로컬 영역은 여러 개의 작은 GTO 장치로 구성되며 di/dt로 인한 과부하 및 과열은 이러한 작은 GTO 장치로 분산됩니다. GTO의 부피는 SCR보다 훨씬 작기 때문에 용량 밀도는 SCR보다 높습니다. 동시에 GTO는 정류 회로가 필요하지 않으므로 1kHz 이상의 응용 프로그램에서 사용할 수 있지만 SCR은 1kHz 내에서만 사용할 수 있습니다. 그러나 GTO의 역 차단 능력은 SCR보다 약하며 보통 20-30V이다. 이러한 장점 때문에 GTO는 메가와트 수준 이상의 고 전력 애플리케이션에 널리 사용됩니다.

일반적으로 파워 다이오드는 스위칭 특성을 최적화하기 위해 GTO에 약 병렬로 연결됩니다. 설계 및 사용을 용이하게 하기 위해 전력 다이오드는 일반적으로 GTO에 통합되어 역전도 사이리스터와 약간 유사한 역전도 GTO를 형성합니다. 역전도 GTO는 더 이상 역전압을 견딜 수 없습니다. 역전압을 견뎌야 하는 경우 직렬로 전원 다이오드가 필요합니다.

5.2.2.2 GTO의 작동 원리

GTO의 켜짐 원리는 사이리스터의 켜짐 원리와 유사합니다. N+ 영역은 전도도 감소에 기여하여 포지티브 피드백 프로세스의 속도를 높입니다. GTO의 α1은 작게 설계되어 GTO의 포화 깊이가 SCR보다 얕아져서 잘리기 쉽습니다 -- SCR이 켜져 있을 때 α1 + α2 ≥ 1.15; GTO가 켜져 있을 때 α1 + α2 ≈ 1.05로 임계 포화에 가깝습니다. 이 설계는 등가 트랜지스터 V2를 게이트 제어 신호에 더 민감하게 만들어 V2를 쉽게 켜고 끌 수 있도록 하지만 동시에 또한 GTO의 온 상태 전압 강하를 증가시킵니다. 턴 오프 과정에서 충분히 큰 음의 전류가 게이트로 흘러 P 베이스 영역의 정공을 소모하고 N- 베이스 영역에 많은 수의 자유 전자를 주입하고 P+ 영역의 정공이 게이트로 주입됩니다. 기본 영역이 감소하고 IC1이 점차 감소하고 IC2도 감소합니다. 일련의 포지티브 피드백 과정 후, 양극 전류 IA가 유지 전류 IH보다 작을 때, GTO는 빠져나가는 포화로 인해 차단됩니다.

* GTO 계산식

GTO의 계산식은 사이리스터의 계산식과 동일합니다.

IC1 = α1 * IA + ICBO1, (10)

IC2 = α2 * IK + ICBO2, (11)

IK = IA + IG, (12)

IA = IC1 + IC2, (13)

IA = (α2 * IG + ICBO1 + ICBO2) /[1 - (α1 + α2) ]. (14)

|IGRP|>(α1 + α2-1) * IATO/α2, (15)

βoff=IATO/|IGRP|. (16)

공식 14에서 볼 수 있습니다.

α1+α2가 0에 접근하면 IA는 전류가 누출되는 경향이 있습니다.

α1+α2가 1에 접근하면 IA는 무한대가 되는 경향이 있습니다.

5.2.3 GTO의 주요 매개변수

GTO의 대부분의 매개변수는 SCR의 주요 매개변수와 동일합니다.

1- 켜짐 시간 t켜기

켜짐 시간 ton은 지연 시간 td와 상승 시간 tr의 합입니다.

2- 꺼짐 시간 t꺼짐

꺼짐 시간 toff는 저장 시간 ts와 하강 시간 tf의 합입니다.

3- 최대 제어 가능한 양극 전류 IATO

최대 제어 가능한 양극 전류 IATO는 GTO의 정격 전류입니다. 양극 전류 IA가 IATO보다 크면 α1 + α2는 조건을 약간 충족할 수 없습니다. 1보다 크면 채도가 깊어져 GTO를 정상적으로 끌 수 없습니다.

4- 현재 턴 오프 이득 βoff

전류 차단 이득 βoff는 최대 제어 가능한 양극 전류 IATO 대 피크 게이트 음의 펄스 전류 IGRP의 비율입니다. β꺼짐=IATO/IGRP. GTO의 βoff가 너무 작기 때문에(보통 3-8), GTO는 게이트에 매우 큰 음의 전류를 인가해야만 차단될 수 있습니다. 이는 제어를 위해 강한 전류를 사용하는 것과 같습니다. 강한 전류. 예를 들어, 정격 전류가 1000A인 GTO에는 300A의 게이트 턴 오프 전류가 필요합니다. 이 주요 단점은 GTO의 적용을 제한합니다.

5.2.4 GTO의 기본 특성

5.2.4.1 GTO의 정적 특성

GTO의 정적 특성은 SCR의 정적 특성과 동일하지만 래칭 전류 IL GTO의 (2A)는 SCR(100-500mA)보다 큽니다.

5.2.4.2 GTO의 동적 특성

1- 켜기 프로세스

UAK=100% UAK1 및 UG ≥ UGT일 때 SCR의 켜기 프로세스와 유사합니다, GTO는 전도 상태로 들어가고 출력 단자는 작은 온 상태 전압 강하를 생성합니다. 그러나 GTO의 다중 유닛 구조로 인해 게이트 트리거 전류 IGT가 SCR보다 높습니다. GTO의 지연 시간 td는 약 1-2μs입니다. GTO의 상승 시간 tr은 온 상태의 양극 전류가 증가함에 따라 증가합니다.

2- 종료 프로세스

SCR과 달리 음의 펄스 전압이 게이트에 적용되어 충분히 큰 음의 펄스 전류를 제공하면 GTO가 턴 오프 프로세스에 들어갑니다. GTO의 턴 오프 과정은 저장시간 ts, 하강시간 tf, 테일 타임 tt로 구분된다.

저장 시간 ts는 IA가 100% IA1에서 90% IA1. 턴 오프 신호 UG2가 인가되면 음의 게이트 전류가 0에서 IGRP로 급격히 상승합니다. 음의 게이트 전류의 di/dt는 회로 인덕턴스와 양극 전압에 따라 달라집니다. 음의 게이트 전류는 포화 전도 동안 저장된 캐리어를 GTO의 P 베이스 영역에서 추출하여 등가 트랜지스터 V2가 포화 상태를 종료하도록 합니다. 이 기간 동안 GTO는 포화 상태를 완전히 벗어나지 않았으므로 UAK 및 IA는 변경되지 않은 상태로 유지됩니다.

하강 시간 tf는 IA가 90% IA1에서 10% IA1. 음의 펄스 전류가 IGRP에 도달하면 양극 전류 IA가 급격히 떨어지기 시작하고 양극 전압 UAK가 상승하기 시작합니다. 베이스 영역의 전도도가 감소함에 따라, α1 + α2≤1, GTO는 턴 오프 상태로 들어가기 시작합니다. 하강 시간 tf는 매우 짧고(약 2μ s) IA의 하강률은 매우 크므로 출력 단자에 스파이크 전압이 발생합니다. GTO.

테일 타임 tt는 IA가 10% IA1에서 0으로 감소하는 데 필요한 시간입니다. 이 기간 동안 나머지 캐리어는 UAK는 점차 UAK1로 상승하고 IA는 점차 0으로 감소합니다. 스너버 회로로 인해 GTO의 출력 단자에서 과도 오버슈트. UAK의 전압 상승률이 너무 크면 GTO가 다시 켜질 수 있습니다. 적절한 게이트 네거티브 펄스를 유지함으로써 테일 타임 tt를 효과적으로 단축할 수 있습니다.

일반적으로 하강 시간 tf는 저장 시간 ts보다 작고 저장 시간 ts는 테일 시간 t보다 작습니다. t, 즉 tf<ts<tt. IA가 10% IA1로 떨어지면 GTO가 차단된 것으로 간주할 수 있으므로 종료 시간에 대한 계산식은 다음과 같습니다. t꺼짐 = ts + tf.

5.3 거대 트랜지스터

5.3.1 GTR 소개

<

GTR(Giant Transistor)은 1970년대에 탄생했으며 고전압 및 그 전류이므로 GTR은 전력 BJT라고도 합니다. GTR의 스위칭 시간은 사이리스터 및 GTO의 스위칭 시간(보통 몇 마이크로초)보다 훨씬 짧으므로 GTR의 작동 주파수가 더 높습니다. 사이리스터의 작동 주파수는 일반적으로 수십 Hz입니다. GTO의 작동 주파수는 일반적으로 수백 Hz입니다. GTR의 작동 주파수는 일반적으로 1-20kHz입니다. GTR의 전력 용량은 1800V/800A/2kHz, 1400v/600A/5kHz, 600V/3A/100kHz와 같이 매우 큽니다. GTR은 낮은 포화 전압, 우수한 스위칭 특성, 넓은 안전 동작 영역, 큰 전력 용량 및 강력한 자체 차단 기능 등의 장점을 가지고 있으므로 GTR은 사이리스터를 대체하여 중형에서 널리 사용됩니다. 전원 공급 장치, 모터 제어 및 일반 인버터와 같은 용량 및 중주파 분야. 그러나 GTR이 요구하는 구동력은 크고 구동회로의 설계는 매우 복잡하다. 동시에 GTR은 서지 전류 저항이 약하고 2차 항복에 쉽게 손상됩니다. 따라서 GTR은 점차적으로 Power MOSFET 및 IGBT로 대체됩니다.

GTR은 구조에 따라 NPN형과 PNP형으로 나눌 수 있다(아래 내용은 NPN형 GTR을 예로 들어 설명한다). GTR은 구조 형태에 따라 단관형 GTR, 달링턴형 GTR(복합 관형 GTR) 및 GTR로 나눌 수 있습니다. 기준 치수. 단관형 GTR은 포화 전압 강하가 낮고 스위칭 속도가 약간 빠르지만 전류 이득 β가 작고(보통 10 정도), 전류 용량이 작고 구동력이 큽니다. 일반적으로 소용량 인버터 회로에 사용됩니다. Darlington 유형 GTR은 큰 전류 이득 β(보통 수십 또는 수백 배까지), 큰 전류 용량, 작은 구동 전력 소비의 장점을 갖지만 포화 전압 강하가 높고 턴 오프 속도가 느립니다.

Darlington 유형 GTR에는 여러 장치가 포함되어 있으며(각 장치는 Darlington 튜브로 구성됨) 이러한 장치는 집적 회로 기술을 통해 병렬로 연결됩니다. GTR 모듈은 2개 이상(4개, 6개 또는 7개)의 단일 튜브 유형 GTR 또는 달링턴 유형 GTR 다이를 단일 튜브 케이스에 캡슐화합니다. GTR 모듈의 GTR 튜브는 단일 브리지 암, 단상 브리지, 3상 브리지 및 블리드 파이프가 있는 삼상 브리지를 형성할 수 있습니다. GTR 모듈은 설계 및 설치가 용이한 하우징 단열재의 장점이 있습니다. 현재 단관형 GTR과 이 모듈식 달링턴형 GTR은 인버터 회로에 거의 사용되지 않는 반면 GTR 모듈은 여전히 널리 사용됩니다.

* Darlington 튜브

달링턴 관운 하프 성관이라고도 합니다. 두 개의 트랜지스터를 직렬로 연결하여 등가 트랜지스터를 형성함으로써 첫 번째 트랜지스터의 출력 신호가 두 번째 트랜지스터의 기본 신호로 사용됩니다. 등가 트랜지스터의 종류는 첫 번째 트랜지스터와 동일하다. 두 트랜지스터 모두 적절한 외부 전압에 의해 증폭 영역에서 작동하므로 이 등가 트랜지스터의 전류 이득은 두 트랜지스터의 전류 이득의 곱입니다. Darlington 튜브는 일반적으로 고 전력 스위칭 회로, 전력 증폭기 및 조정 전원 공급 장치와 같은 매우 민감한 증폭 회로에서 매우 작은 신호를 증폭하는 데 사용됩니다.

5.3.2 GTR은 어떻게 작동합니까?

5.3.2.1 GTR의 기본 구조

GTR의 구조는 BJT의 구조와 유사합니다. NPN 유형 GTR은 두 개의 PN 접합(컬렉터 접합 J1 및 이미터 접합 J2)에 의해 이미터 영역, 베이스 영역 및 컬렉터 영역으로 나뉩니다. 면적 및 높은 도핑 농도; 베이스 영역은 얇은 두께(5-20μ m)와 낮은 도핑 농도를 가지고 있습니다. 컬렉터 영역은 두 부분으로 나뉩니다. N- 컬렉터 드리프트 영역은 면적이 크고 도핑 농도가 낮고 N+ 기판 영역은 면적이 작고 도핑 농도가 높습니다.

5.3.2.2 GTR의 작동 원리

GTR의 작동 원리 및 계산식은 BJT의 작동 원리 및 계산식과 동일합니다. 그러나 턴 온 프로세스 동안 N+ 기판 영역은 J1의 역전류를 증가시키기 위해 N- 드리프트 영역으로 많은 수의 자유 전자를 주입한다는 점에 유의해야 합니다.

5.3.3 GTR의 주요 매개변수

GTR의 대부분의 매개변수는 BJT의 주요 매개변수와 동일합니다.

1- 항복 전압 BV

GTR의 출력에 인가되는 전압 UCE가 규정된 값을 초과하면 GTR을 항복시키고 이 전압을 항복 전압 BV라 한다. 항복 전압은 그림 33과 같이 GTR의 특성뿐만 아니라 외부 회로의 연결 방식과도 관련이 있습니다.

BVCBO는 이미 터가 열려 있을 때 컬렉터와 베이스 사이의 역 항복 전압입니다.

BVCEO는 베이스가 열려 있을 때 컬렉터와 이미 터 사이의 항복 전압입니다.

BVCER은 이미터와 베이스가 저항으로 연결된 경우 컬렉터와 이미터 사이의 항복 전압입니다.

BVCES는 이미터와 베이스가 단락 되었을 때 컬렉터와 이미터 사이의 항복 전압입니다.

BVCEX는 이미터 접합이 역 바이 어스될 때 컬렉터와 이미터 사이의 항복 전압입니다.

이러한 항복 전압은 다음과 같은 관계를 갖습니다.

BVCBO>BVCEX>BVCES>BVCER>BVCEO

안전을 위해 실제 공정에서 최대 작동 전압은 BVCEO보다 훨씬 낮은 것을 권장합니다.

2- 최대 컬렉터-이미터 전압 UCEM

최대 컬렉터-이미터 전압 UCEM은 GTR의 정격 전압입니다. 안전한 사용을 위해 최대 작동 전압 UCEM은 항복 전압 BVCEO보다 낮습니다.

3-초 고장 전력 PSB

2차 항복은 주로 고전압, 더 전류의 경우에 발생하며, 해당 2차 항복 내력을 2차 항복 전원 PSB라고 합니다.

5.3.4 GTR의 기본 특성

5.3.4.1 GTR의 정적 특성

GTR의 정적 특성은 BJT의 정적 특성과 유사합니다. 차이점은 저전류 BJT는 증폭 영역에서 작동하는 반면 GTR은 포화 영역과 차단 영역에서만 작동한다는 것입니다(즉, GTR은 켜짐 및 꺼짐 상태만 있고 도즈에는 증폭 상태가 없습니다. ). GTR이 증폭된 상태에서 작동할 때 전류가 매우 크고 소비 전력도 크기 때문에 GTR이 심한 열로 인해 쉽게 소손되기 때문입니다. 그러나 스위칭 과정(온 상태에서 오프 상태로 왔다 갔다 하는 과정)에서 GTR은 증폭 영역을 통과해야 한다. 일반적으로 이 프로세스는 GTR의 손상을 방지하기 위해 매우 빠릅니다.

5.3.4.2 GTR의 동적 특성

GTR의 동적 특성은 BJT의 동적 특성과 유사합니다.

1- 켜기 프로세스

순방향 베이스 전류 IB1를 적용하면 GTR이 전도 상태로 들어갑니다. 켜짐 과정은 지연 시간 td와 상승 시간 tr로 나뉩니다.

켜짐 시간의 계산 공식: ton = td + tr

2- 종료 프로세스

베이스 전류 IB를 끄면 GTR을 차단할 수 있습니다. 그리고 역전류는 턴 오프 프로세스의 속도를 높일 수 있습니다. 꺼짐 과정은 저장 시간 ts와 하강 시간 tf로 나뉩니다.

꺼짐 시간의 계산 공식: toff=ts + tf

* GTR 켜기 프로세스의 속도를 높이는 방법

● 가속 커패시터를 추가합니다. GTR의 베이스 저항 양단에 커패시터를 병렬로 연결하고, 커패시터 전압이 정류 순간에 갑자기 변하지 않는 특성을 이용하여 GTR의 스위칭 특성을 향상시킨다. 물론 접합 커패시턴스가 상대적으로 작은 고속 스위치 GTR 튜브도 선택할 수 있습니다.

● 드라이브 속도를 높입니다. GTR이 켜져 있을 때 특정 진폭과 가파른 전방 가장자리를 가진 순방향 구동 전류를 제공함으로써 td 및 tr을 감소시켜 회전을 가속화할 수 있습니다. GTR의 프로세스를 켜고 켜기 시간을 단축합니다. ton. 그러나 구동 전류가 너무 커서는 안 됩니다. 그렇지 않으면 과포화로 인해 GTR의 확산 시간 ts가 증가합니다.

* GTR 종료 프로세스의 속도를 높이는 방법

● 채도 깊이를 줄입니다. 턴 온 과정에서 포화 깊이를 줄임으로써 베이스에 저장되는 캐리어를 줄여 GTR의 저장 시간 ts를 단축할 수 있습니다.

● 음의 구동 전류 IB2를 적용합니다. GTR이 꺼져 있을 때 특정 진폭과 오버슈트의 음의 구동 전류를 인가함으로써 베이스에서 캐리어를 추출하는 속도를 가속화하여 GTR의 저장 시간 ts를 단축할 수 있습니다.

● 역 베이스 전압 UB2를 적용합니다. GTR이 꺼지면 역 베이스 전압을 증가시켜 GTR의 저장 시간 ts를 단축함으로써 저장된 전하의 소산을 가속화할 수 있습니다. 그러나 역 베이스 전압은 이미 터 접합의 파괴를 피하기 위해 너무 커서는 안됩니다.

3- GTR의 두 번째 고장 현상

첫 번째 고장: 컬렉터 전압이 항복 전압 BVCEO를 초과하면 GTR이 분해됩니다. -- IC가 급격히 증가하고 출력 전압 UCE GTR의 는 특정 값(즉, 유지 전압 BVsus)으로 유지됩니다. 첫 번째 항복이 발생할 때 외부 회로가 항복 후 전류를 제한할 수 있는 한 GTR은 손상되지 않습니다. 컬렉터 전압이 BVCEO 미만으로 감소한 후 GTR은 정상으로 돌아가고 작동 특성은 변경되지 않습니다. 따라서 첫 번째 고장은 되돌릴 수 있으며 GTR에 손상을 줄 수 없습니다.

두 번째 고장: 첫 번째 고장이 발생할 때 전류 제한 조치를 즉시 취하지 않으면 컬렉터 전류 IC가 두 번째 고장 ISB의 임계점에 도달하게 됩니다. GTR의 국부 전류 밀도를 증가시킵니다. 국부적으로 가열되고 국부 전류 밀도를 더욱 증가시킬 것이다. 일련의 포지티브 피드백 이후 GTR의 표면 온도가 높지는 않지만 고온으로 인해 내부의 국부적인 부분이 손상되고 컬렉터와 이미터 사이에 낮은 저항 채널이 형성되고 컬렉터 전압 U CE가 떨어지고 컬렉터 전류 IC가 급격히 상승합니다. 이 현상을 2차 고장이라고 합니다. 두 번째 고장은 되돌릴 수 없으며 GTR에 영구적인 손상을 일으키고 작업 특성을 크게 저하시킵니다.

4- GTR의 안전한 작동 영역

최대 전압 UCEM, 최대 컬렉터 전류 ICM, 최대 소산 전력 PCM 및 두 번째 항복 전력 P SB는 두 번째 고장 임계선을 구성합니다. 두 번째 항복 이미 계선에서 그림자로 표시된 영역이 안전 작동 영역입니다.

5.4 전력 MOSFET

5.4.1 MOSFET 소개

전계 효과 트랜지스터(FET)는 전압에 의해 제어되는 단극 소자입니다. FET의 작동 원리는 주로 전기장을 사용하여 반도체의 전도성 채널을 형성하여 반도체의 전도성을 제어하는 것입니다. FET는 접합 FET(JFET, SIT라고도 함)와 절연 게이트 FET로 나눌 수 있습니다.

금속 산화물 반도체 전계 효과 트랜지스터(MOSFET)는 금속, 산화물 및 반도체로 만들어진 절연 게이트 전계 효과 트랜지스터입니다. MOSFET은 매우 중요한 전력 전자 장치입니다. MOSFET은 높은 입력 임피던스(약 107-1015Ω), 저 잡음, 저전력 소비, 넓은 동적 범위, 우수한 온도 특성, 통합하기 쉽고, 2차 항복 현상이 없고, 간단한 구동 회로, 작은 구동 전력, 빠른 스위칭 속도, 높은 작동 주파수, 우수한 열 안정성(GTR보다 우수), 넓은 안전 작동 영역 및 게이트 바이어스는 양수 또는 음수 또는 0일 수 있습니다. 이러한 장점으로 인해 MOSFET은 신호 증폭, 임피던스 변환, 가변 저항, 정전류 소스, 전자 스위치 등과 같은 회로에 널리 사용됩니다. 다른 전력 전자 장치에 비해 작은 전류 용량과 낮은 저항으로 인해 MOSFET의 전압인 다중 유닛 통합 메커니즘은 일반적으로 1kW 이하의 고주파 전력 전자 기기에 주로 사용되는 고 전력 용량의 Power MOSFET을 형성하는 데 사용됩니다. MOSFET은 주로 DC 솔리드스테이트 릴레이에 사용됩니다(클릭하여 더 많은 DC 솔리드스테이트 릴레이 보기).

5.4.2 MOSFET은 어떻게 작동합니까?

5.4.2.1 MOSFET의 기본 구조

MOSFET에는 게이트(G), 드레인(D), 소스(S), 보디(B)의 4가지 단자가 있습니다. MOSFET의 주요 구조는 기판(본체 또는 베이스라고도 함)이며, 그 주요 재료는 실리콘입니다. 소스와 드레인 사이에 산화물 절면 층(게이트 산화층 또는 게이트 절면 층이라고도 함)이 있으며, 그 재료는 일반적으로 SiO2입니다. 게이트는 게이트 절연층 위에 있으며, 그 재료는 알루미늄(알루미늄 게이트)이었으나 지금은 폴리실리콘(폴리실리콘 게이트)입니다. MOSFET 게이트의 내부 저항은 수백 메가 옴까지 매우 높기 때문에 게이트, 소스, 드레인 및 기판 사이에 전도가 없습니다. 실제 사용에서 전력 다이오드는 일반적으로 MOSFET의 드레인과 소스 사이에 병렬로 연결되어 회로의 순간적인 역전류가 MOSFET을 파괴하는 것을 방지합니다. 일반적으로 전력 다이오드는 MOSFET에 직접 통합됩니다.

MOSFET은 기판의 재질에 따라 N-MOSFET(또는 N-MOS)와 P-MOSFET(또는 P-MOS)로 나눌 수 있습니다. N-MOS는 P형 기판을 사용하며 소스는 회로의 가장 낮은 전위에 연결되어야 합니다. P-MOS는 N형 기판을 사용하며 그 소스는 회로의 가장 높은 전위에 연결되어야 합니다.

게이트 전압이 0일 때 소스와 드레인 사이에 전도성 채널이 있는지에 따라 MOSFET은 강화형 MOSFET과 공핍형 MOSFET으로 나눌 수 있습니다.

MOSFET의 구조는 소스와 드레인이 같은 평면에 있는지에 따라 수직 구조와 수평 구조로 나눌 수 있습니다.

여기에 나열할 수 없는 많은 분기 유형 및 MOSFET의 파생 장치가 있습니다. 다음은 LDMOSFET, CMOS 및 VDMOSFET에 대한 소개입니다.

1- LDMOSFET

LDMOSFET의 소스(S)와 드레인(D)은 동일한 평면에 있으므로 별도의 보디(B)가 필요합니다. N 채널 LDMOSFET를 예로 들어 보겠습니다(그림 39 참조). 그 기질은 P-기질 영역이고 전도에 관여하는 캐리어는 자유 전자입니다. P- 서브 스테이트 영역(P-Sub)에는 2개의 고도로 도핑 된 N+ 영역이 있으며, 그중 하나는 소스 영역이라고 하고 다른 하나는 드레인 영역이라고 합니다. 이 두 영역은 정확히 동일하며 이론적으로 두 영역을 바꾸는 데 문제가 없습니다. 소스(S)와 드레인(D) 이 같은 평면에 있기 때문에 보디 효과로 인한 임계 전압 이동은 발생하다. 따라서 P-기판 영역에 고 도핑 된 P+ 영역을 추가함으로써 몸체(B)가 P+ 영역에서 소스(S)로 연결되어 몸체의 전위가 소스의 전위와 같게 됩니다. , 신체 효과를 피할 수 있습니다. LDMOSFET의 전도성 채널은 기판에 형성됩니다. 향상된 N-채널 LDMOSFET의 게이트 전압이 0일 때 그림 39, a와 같이 소스와 드레인 사이에 채널이 없습니다. 공핍 N-채널 LDMOSFET의 게이트 전압이 0일 때 그림 39, b에서와 같이 소스와 드레인 사이에 채널이 있습니다. 측면 치수(수평 영역)를 늘리면 LDMOSFET의 채널 길이가 늘어납니다. 그러나 수평 영역의 증가는 LDMOSFET의 온 저항의 증가로 이어질 것입니다.

* 전도성 채널의 길이와 너비

소스 영역과 드레인 영역 사이의 거리를 전도성 채널 길이라고 합니다. L그린 = Leff + 2 * LD. L그린은 총 채널 길이, Leff는 유효 채널 길이, LD는 측면 확산 길이입니다. 게이트에서 전도성 채널의 바닥까지의 거리를 전도성 채널 너비라고 합니다. 전도성 채널의 길이(L)와 너비(W)는 MOSFET의 채널 저항을 결정합니다.

* 바디 효과

바디 효과는 기판 전압이 소스 전압보다 낮아진 후 전도성 채널에서 공핍 영역의 폭이 넓어져 임계 전압이 높아지는 것을 말합니다.

2- CMOS

CMOS는 집적 회로에서 가장 일반적으로 사용되는 프로세스 중 하나입니다. 단일 실리콘 칩에 여러 N-MOS 및 P-MOS를 통합할 수 있습니다. P-MOS는 N-MOS에 직접 내장되어 있으므로 P-MOS의 기판을 N-well이라고도 합니다. CMOS는 고효율, 저전력 소모, 고 임피던스, 복잡한 논리 처리 능력 등의 장점이 있습니다.

3- VDMOSFET

수직 이중 확산 MOSFET(VDMOSFET)은 가장 일반적인 전력 MOSFET입니다(그림 41은 향상된 N-채널 VDMOSFET를 보여줍니다). VDMOSFET의 소스와 드레인은 동일한 평면에 있지 않으므로 별도의 본체(B)가 필요하지 않습니다. 수평 영역을 늘리지 않고 수직 치수(수직 영역)를 늘리면 채널 길이가 VDMOSFET가 증가합니다. 따라서 온 저항이 동일한 MOSFET의 경우 VDMOSFET는 LDMOSFET보다 더 높은 전류 내성을 갖습니다. VDMOSFET의 등가 저항을 증가시키는 VDMOSFET의 P 영역과 N 영역 사이에 낮은 도핑 농도를 갖는 N-에피택셜 영역의 추가 층이 있기 때문에 VDMOSFET는 더 높은 전압을 견딜 수 있습니다. 컨덕턴스 변조 효과로 인해 PN 접합을 통해 흐르는 전류가 점차 증가하면 N-에피택셜 영역의 내부 저항이 감소하지만 VDMOSFET의 내전압 성능은 여전히 LDMOSFET보다 큽니다. 또한 N 영역과 P 영역은 기생 전력 다이오드를 형성하여 역전압 항복으로부터 VDMOSFET를 효과적으로 보호할 수 있습니다. 따라서 대부분의 전력 MOSFET은 더 나은 내전압 및 전류 성능을 얻기 위해 수직 구조를 채택합니다.

홈 게이트의 모양에 따라 VDMOSFET는 VVDMOS(v-groove 수직 이중 확산 MOSFET 또는 v-groove 수직 채널 이중 확산 MOSFET, VMOS라고도 함)와 UVDMOS(u-groove 수직이라고도 함)로 나눌 수 있습니다. 이중 확산 MOSFET 또는 u-그루브 수직 채널 이중 확산 MOSFET, UMOS). UMOS는 VMOS보다 더 나은 내전압 기능을 가지고 있습니다. VMOS는 전력 전자 분야에서 매우 널리 사용되기 때문에 일반적으로 전력 MOSFET은 VMOS를 의미합니다.

5.4.2.3 MOSFET의 작동 원리

MOSFET의 작동 원리는 외부 전기장을 인가하여 반도체 내부의 전도도를 변경하는 것입니다. P-MOSFET의 작동 원리는 N-MOSFET의 작동 원리와 정확히 동일합니다. 또한 VDMOSFET와 LDMOSFET의 작동 원리는 유사하지만 측면 구조로 인해 MOSFET 내부의 전류 변화를 명확하게 관찰할 수 있습니다. 따라서 다음은 N-채널 LDMOSFET를 예로 들어 MOSFET의 작동 원리를 소개합니다.

1- 강화형 MOSFET

게이트 전압이 인가되지 않을 때(UGS=0), 인핸스먼트형 MOSFET의 소스 영역과 드레인 영역 사이에 전도성 채널이 없고 전도성 채널은 특정 게이트 전압이 적용됩니다. 따라서 강화형 MOSFET은 NC(Normally Closed) 소자입니다.

축적층 단계: UGS<0일 때 반도체 표면에 수직인 전기장이 게이트에서 생성되어 P-영역의 정공을 절연층 바닥으로 끌어당기고 P-영역에서 자유전자를 밀어내고 축적 측을 형성한다. 소스와 드레인 사이에 양의 전압이 인가되더라도 드레인에서 소스로 직접 전류가 흐를 수 없습니다(누설 전류는 고려되지 않음), 따라서 MOSFET은 오프 상태에 있습니다.

공핍층 단계: 0<UGS<UT일 때 반도체 표면에 수직인 전기장이 게이트에서 생성되어 반도체 표면의 자유 전자를 끌어당깁니다. 절연층의 바닥에 P-영역을 형성하고 P-영역의 정공을 밀어내고 공핍층을 형성한다. 그러나 절연층 바닥에 축적된 자유전자가 너무 적어 전도성 채널을 형성하지 못하기 때문에 MOSFET은 여전히 오프 상태이다.

반전층 단계: UGST일 때 절연층의 바닥에 축적된 자유전자는 N형 좁은 층(즉, N 유형 전도성 채널). N형 도전성 채널의 형태가 P-영역과 반대이기 때문에 반한 층(inversion layer)이라고도 한다. 전도성 채널의 존재는 전류가 드레인 영역에서 소스 영역으로 흐를 수 있도록 하므로 MOSFET은 온 상태입니다. UGS의 증가에 따라 게이트에 의해 형성되는 전계가 강할수록 더 많은 자유 전자가 절연층의 바닥으로 끌리게 됩니다. 전도성 채널이 넓을수록 채널 저항이 작아지고, 그리고 더 큰 드레인 전류 ID. 채널을 따라 드레인 전류 ID에 의해 생성된 전압 강하는 채널의 각 지점과 게이트 사이의 전압을 더 이상 동일하지 않게 만듭니다. 소스 영역에 가까울수록 전압 강하가 클수록 채널이 넓어집니다. 드레인 영역에 가까울수록 전압 강하가 작아지고 채널이 좁아집니다. 드레인 영역에 가장 가까운 끝에서 전압 강하는 가장 작고(그 값은 UGD= UGS - UDS임), 채널이 가장 좁습니다. 그리고 UDS가 증가함에 따라 드레인 영역 근처의 채널은 점점 좁아집니다.

핀치오프 영역 단계: MOSFET이 켜져 있을 때 UGD = UGS-UDS = UT가 될 때까지 UDS가 계속 증가하면 드레인 영역이 0이 되어 강한 반전 채널을 형성할 수 없습니다. 즉, 채널이 핀치오프됩니다. 채널의 너비가 0인 지점을 핀치오프 지점이라고 하고 핀치오프 지점과 드레인 영역 사이의 공핍 영역을 핀치오프 영역이라고 합니다. UDS가 계속 증가하면 핀치오프 지점이 소스 영역으로 이동합니다. UDS의 증가는 거의 핀치오프 영역에 적용되므로 핀치오프 영역도 계속 확장됩니다. 채널이 핀치 오프된 후 드레인 전압이 계속 증가하더라도 드레인 전류는 일정한 값(즉, 포화 드레인 전류 ID(sat))으로 유지되고 MOSFET은 포화 상태에서. 포화 드레인 전류 ID(sat)는 UDS의 영향을 받지 않지만 UGS에 의해 결정됩니다. -- ID(sat)는 MOSFET 제곱법칙 전달 특성인 UGS의 제곱과의 관계.

2- 공핍형 MOSFET

게이트 전압이 인가되지 않을 때(UGS=0), 공핍 MOSFET의 소스 영역과 드레인 영역 사이에 전도성 채널이 있습니다. 순방향 게이트 전압이 인가되면 전도성 채널의 폭이 증가합니다. 역 게이트 전압이 인가되면 전도성 채널의 폭이 감소합니다. 역 게이트 전압이 특정 값에 도달하면 전도성 채널이 사라집니다. 따라서 공핍 N-MOSFET은 NO(Normally Open) 소자입니다.

전도 상태: UGS≥0일 때 게이트에서 생성된 전기장은 N 채널로 더 많은 전자를 끌어당기고 N 채널의 정공을 밀어냅니다. UGS가 증가할수록 채널이 넓어지고 채널 저항이 작아지며 ID가 증가합니다.

차단 상태: UGS<0일 때 게이트에서 생성된 전기장은 N 채널로 더 많은 정공을 끌어당기고 N 채널에서 전자를 밀어내어 채널을 더 좁게 만들고 채널을 저항이 커집니다. UGS가 핀치오프 전압 UPO에 도달하면 N 채널의 전자가 고갈되고 전도성 채널이 사라지며 ID 제로 경향이 있습니다.

5.4.3 MOSFET의 주요 파라미터

MOSFET의 대부분의 매개변수는 BJT의 주요 매개변수와 동일합니다.

1- 트랜스 컨덕턴스 Gfs

일반적으로 입력 전압에 대한 입력 전류의 비율을 어드미턴스라고 합니다. MOSFET의 전달 특성으로 인해 게이트-소스 입력 전압 UGS는 게이트-소스 입력 전류 IGS의 변화에 영향을 미치지 않지만 드레인의 변화에는 영향을 미칩니다. 전류 iD이므로 드레인 전류 ID 대 게이트-소스 전압 UGS의 비율을 트랜스 컨덕턴스라고 합니다.

2- 기생 커패시턴스

MOSFET 내부에는 세 가지 내부 기생 커패시턴스가 있습니다. 게이트-소스 기생 커패시턴스 CGS, 게이트-드레인 기생 커패시턴스 CGD(밀러 커패시턴스라고도 함), 드레인-소스 기생 커패시턴스 CDS. 이러한 기생 커패시턴스는 MOSFET의 동적 특성에 영향을 미칩니다. 기생 커패시턴스가 작으면 스위칭 전류와 구동 전력이 작고 스위칭 속도가 빠릅니다. 기생 커패시턴스가 크면 스위칭 전류와 구동 전력이 크고 스위칭 속도가 느립니다. MOSFET 제조업체는 일반적으로 다음 계산 공식을 충족하는 MOSFET의 커패시턴스 매개변수를 제공합니다.

MOSFET의 입력 커패시턴스: Ciss = CGS + CGD

MOSFET의 출력 커패시턴스: Coss = CDS + CGD

MOSFET의 역방향 전달 커패시턴스: Crss = CGD

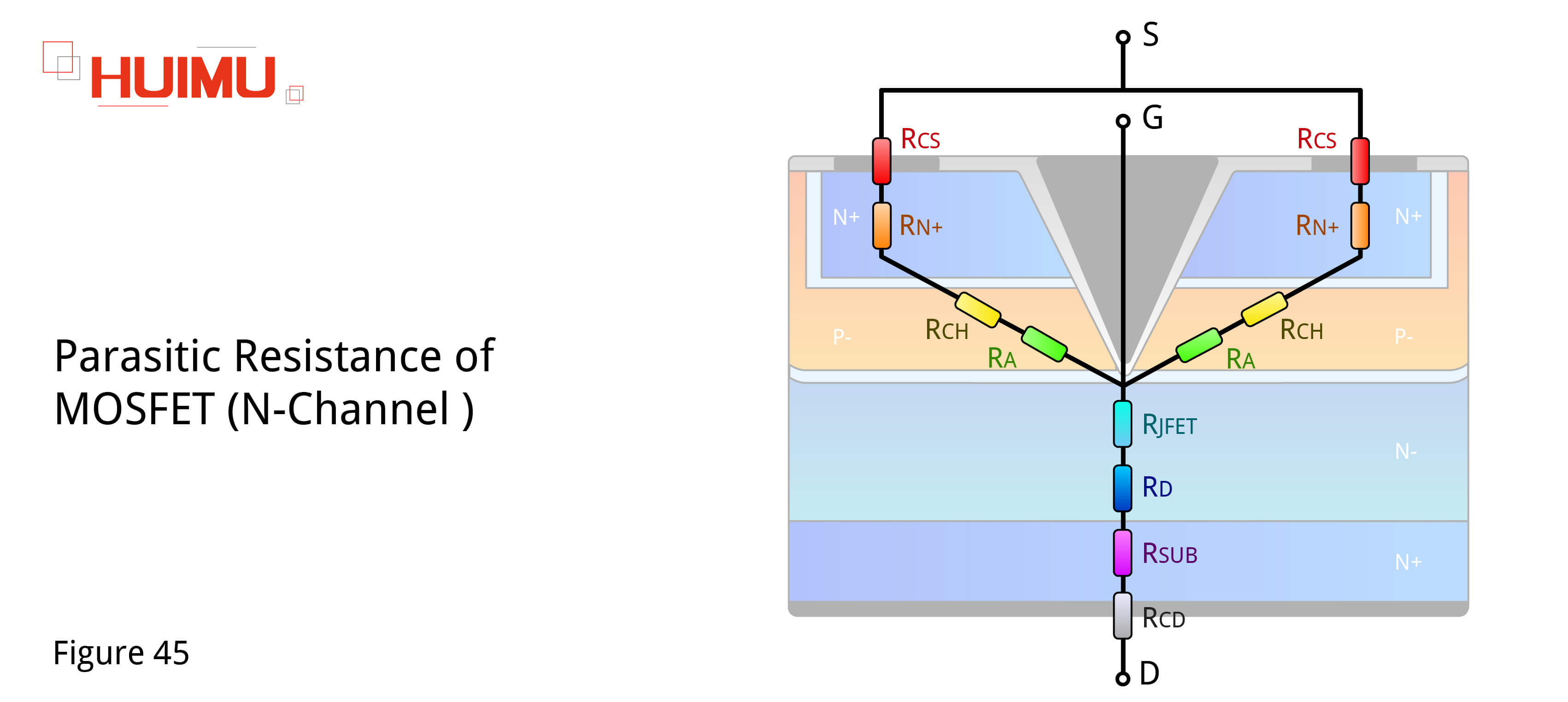

3- 드레인 소스 온 저항 RDS(on)

드레인-소스 온 저항 RDS(on)는 특정 조건에서 MOSFET이 켜질 때 MOSFET의 드레인과 소스 사이의 온 저항을 나타냅니다. RDS(on)는 MOSFET의 기생 저항에 의해 결정됩니다. RDS(on) = RCS + RN+ + RCH + RA + RJFET + RD + RSUB + RCD. RCS는 N+ 소스 영역과 소스 전극 사이의 접촉 저항입니다. RN+는 N+ 소스 영역과 채널 사이의 저항입니다. RCH는 채널의 저항입니다. RA는 축적 층위 저항입니다. RJFET는 동등한 JFET의 저항입니다. RD는 드리프트 영역의 저항입니다. RSUB는 기판 영역의 저항입니다. RCD는 기판 영역과 드레인 전극 사이의 접촉 저항입니다. 드레인-소스 온 저항 RDS(on)은 MOSFET 접합 온도와 게이트-소스 전압(구동 전압) UGS의 영향을 받습니다. 접합 온도가 높을수록 RDS(on)가 커집니다. 반대로 더 작은 RDS(on). 게이트-소스 전압이 높을수록 RDS(on)가 작아집니다. 반대로 RDS(on)가 더 커집니다.

4- 최대 드레인 전류 IDM

최대 드레인 전류 IDM은 MOSFET의 정격 전류입니다. 최대 드레인 전류는 케이스 온도가 특정 값일 때 MOSFET이 가장 높은 접합 온도에 도달할 수 있도록 하는 드레인 전류를 나타냅니다. 최대 드레인 전류는 MOSFET의 구조뿐만 아니라 MOSFET의 패키징 방식 및 주변 온도와도 관련이 있습니다.

5- 최대 드레인 소스 전압 BVDSS

최대 드레인-소스 전압 BVDSS는 MOSFET의 정격 전압입니다. 최대 드레인-소스 전압은 주변 온도가 25°C 일 때 MOSFET 드레인 및 소스가 애벌 런치 항복을 겪지 않을 때 인가할 수 있는 최대 전압을 나타냅니다. 실제 동작에서 드레인 전류가 250μ A 일 때 측정된 드레인-소스 전압 값은 일반적으로 최대 드레인-소스 전압 BVDSS로 간주됩니다.

6- 최대 게이트 소스 전압 UGSM

최대 게이트-소스 전압(최대 구동 전압이라고도 함)은 매우 짧은 시간에 MOSFET의 게이트 절연층에 영구적인 손상을 줄 수 있는 최대 입력 전압을 나타냅니다. 일반적으로 구동 전압은 ±20V를 초과하지 않는 것이 좋습니다.

7- 스위칭 주파수

MOSFET의 스위칭 시간은 10~100μ s이며, 동작 주파수는 주요 전력 전자 장치 중 가장 높은 100kHz(수 MHz까지) 이상에 도달할 수 있습니다. MOSFET은 정적일 때 입력 전류가 거의 필요하지 않지만 동적일 때(스위칭 프로세스) 기생 커패시턴스를 충전 및 방전하므로 특정 구동 전력이 여전히 필요합니다. MOSFET의 스위칭 주파수가 높을수록 더 많은 구동 전력이 필요합니다.

5.4.4 MOSFET의 기본 특성

향상된 N-MOSFET을 예로 들어 보겠습니다. VDD는 MOSFET의 출력 전원입니다. UP는 MOSFET의 구동 신호 소스입니다. UGS는 게이트와 소스 사이의 전압입니다. UDS는 MOSFET의 출력 전압 강하입니다. ID는 드레인 전류입니다. RS는 구동 회로의 내부 저항입니다. RG는 게이트 내부 저항입니다. RL은 배수 부하입니다. RF는 드레인 전류를 감지하는 데 사용되는 감지 저항입니다.

5.4.4.1 MOSFET의 정적 특성

1- 입력 특성

MOSFET의 전달 특성으로 인해 MOSFET의 게이트와 소스 사이의 전압 변화는 게이트와 소스 사이의 전류에는 영향을 미치지 않지만 드레인 전류 ID에는 영향을 미칩니다. ID가 클 때 ID와 UGS 사이의 관계는 대략 선형이고 그 기울기는 MOSFET의 트랜스 컨덕턴스 Gfs입니다.

2- 출력 특성

MOSFET의 정적 출력 특성 곡선은 GTR의 정적 출력 특성 곡선과 유사합니다. MOSFET의 정적 출력 특성은 차단 영역, 포화 영역 및 비포화 영역으로 나눌 수 있습니다. MOSFET은 일반적으로 스위칭 상태(즉, 컷오프 영역과 비포화 영역 사이의 빠른 전환)에서만 작동하여 포화 영역에서 작업할 때 과도한 전력 소모로 인해 MOSFET이 소손되는 것을 방지합니다.

차단 영역: BJT의 차단 영역과 유사합니다. UDS가 매우 높지만 드레인 전류 ID=0(누설 전류는 고려되지 않음)입니다.

포화 영역: BJT의 활성 영역과 유사합니다. ID는 UDS의 영향을 받지 않지만 UGS가 증가함에 따라 증가합니다. 포화 영역에서는 MOSFET이 부담하는 전압과 전류가 크기 때문에 소비 전력이 매우 큽니다.

비포화 영역: BJT의 포화 영역과 유사합니다. ID는 UDS가 증가함에 따라 증가합니다. 비포화 상태에서 MOSFET은 큰 전류와 매우 작은 전압을 견디므로 소비 전력이 적습니다. MOSFET은 비포화 영역에서 전압 제어 저항으로 동작하므로 이 영역을 옴 영역 또는 가변 저항 영역이라고도 합니다.

5.4.4.2 MOSFET의 동적 특성

MOSFET의 스위칭 과정에서 스위칭 시간에 대한 내부 기생 커패시턴스 희 영향은 무시할 수 없습니다.

1- 켜기 프로세스

MOSFET을 온 상태로 전환하려면 게이트에 가파른 입력 전원 UP1을 적용해야 합니다. 구동 회로의 내부 저항 RS와 게이트-소스 기생 정전 용량 CGS의 존재로 인해 게이트 전압 UGS MOSFET의 펄스 파형은 UP1만큼 가파른 펄스 파형을 형성할 수 없지만 특정 기울기로 상승합니다. 구동 전류가 CGS를 충전하기 시작하여 UGS가 UT에 도달하면 MOSFET은 온 상태로 들어가고 드레인 전류 I D가 오르기 시작합니다. CGS가 완전히 충전되면 UGS는 UGS1에서 유지되고 ID는 I에서 유지됩니다. D1. 이때, 드레인-소스 기생 커패시턴스 CDS가 방전되기 시작하고 UDS가 감소하기 시작한다. UDS가 최솟값에 도달하면 구동 전류가 게이트-드레인 기생 커패시턴스 CGD를 충전하기 시작하고 UGS가 UGS2에 남아 있습니다. 일반적으로 UGS에서 10%로 상승하는 시간 UGS2에서 ID에서 10% ID1로 상승하는 시간 켜기 지연 시간 td(on)라고 합니다. ID가 10% ID1에서 90% ID1로 상승하는 데 걸리는 시간을 상승 시간 tr. MOSFET의 턴 온 시간 ton은 턴 온 지연 시간 td(on)와 상승 시간 tr.

켜짐 시간의 계산 공식: ton = td(on) + tr

2- 종료 프로세스

구동 펄스 신호 UP1가 제거되면 RS와 CGD로 인해 UGS가 감소합니다. 특정 경사. CGD가 방전되면 UGS는 UGS1에 머물고 이때 CDS가 충전을 시작합니다. , UDS가 상승하기 시작합니다. CDS가 완전히 충전되면 UDS는 100% UDS1로 유지되며 이때 CGS 방전이 시작되고 UGS가 다시 떨어집니다. UGS가 UT 아래로 떨어지면 MOSFET은 오프 상태로 들어가고 ID는 0으로 떨어집니다. MOSFET은 소수 캐리어 저장 효과가 없기 때문에 턴오프 프로세스가 매우 빠릅니다(약 수십 나노초). 일반적으로 90% UGS2에서 90% ID1까지의 시간을 턴오프 지연 시간 td(off)라고 합니다. ID가 90% ID1에서 10% ID1로 떨어지는 데 걸리는 시간을 하강 시간 tf라고 합니다. MOSFET의 턴오프 시간 ton은 턴오프 지연 시간 td(off)와 하강 시간 tf.

꺼짐 시간의 계산 공식: toff = td(off) + tf

* MOSFET의 스위치 프로세스 속도를 높이는 방법

● 내부 저항과 인덕턴스가 낮은 구동 회로를 사용하면 MOSFET의 턴 온 프로세스를 가속화할 수 있습니다.

● 턴 온 및 턴 오프 프로세스 동안 기생 커패시턴스를 충전 및 방전하는 MOSFET의 기능을 개선하여 지연 시간을 효과적으로 줄여 과도 오류가 발생하지 않도록 할 수 있습니다.

5.4.5 MOSFET의 직렬 및 병렬연결

MOSFET의 스위칭 속도는 매우 빠르고 동적 특성에는 어느 정도 분산이 있기 때문에 일반적인 전압 균등화 방식을 채택하는 것은 불가능합니다. MOSFET을 직렬로 연결하면 스위칭 과정에서 각 MOSFET의 작동 상태가 다르고 내전압 성능을 동일하게 유지할 수 없으므로 내전압이 낮은 MOSFET이 과전압으로 인해 소손되기 쉽습니다. 따라서 MOSFET은 직렬연결에 적합하지 않습니다.

MOSFET의 온 저항은 양의 온도 계수를 가지며 온도가 높을수록 온 저항이 커집니다. 실제 응용 프로그램에서 여러 MOSFET을 병렬로 사용할 수 있습니다. 예를 들어 인버터 용접기의 출력 회로는 수십 개의 MOSFET을 병렬로 연결하여 전류 용량을 늘릴 수 있습니다. MOSFET 중 하나가 너무 많은 전류를 흐르게 하면 온 저항이 클수록 온 저항이 작은 다른 MOSFET에 더 많은 전류가 흐르고 결국 각 MOSFET에 흐르는 전류는 균형을 이루는 경향이 있습니다. 다음 방법은 전류 불균일 현상을 효과적으로 줄일 수 있습니다. 매개변수 오류가 작은 MOSFET을 선택하십시오. 회로의 배선 및 레이아웃은 대칭이어야 합니다. 라인 손실(와이어 자체의 저항이 전류를 소비함)과 고주파에서 와이어의 인덕턴스 및 커패시턴스를 고려해야 합니다. 소스 회로에 작은 인덕터를 연결하면 전류 공유 리액터 역할을 할 수 있으므로 동적 불균일 전류를 효과적으로 줄일 수 있지만 정적 불균일 전류에는 유효하지 않습니다.

5.5 절연 게이트 밤이 폴라 트랜지스터

5.5.1 IGBT 소개

절연 게이트 밤이 폴라 트랜지스터(IGBT 또는 IGT)는 파워 MOSFET의 높은 입력 임피던스와 BJT의 높은 전류 용량을 가진 복합 Bi-MOS 소자입니다. IGBT는 컨버터, 인버터, 펄스 폭 변조 시스템(PWM), 무정전 전원 공급 장치(UPS), 스위칭 모드 전원 공급 장치(SMPS), 공진 변환기, 산업용 모터, 신에너지 자동차 등 많은 분야에서 널리 사용됩니다. IGBT에는 높은 입력 임피던스, 저 잡음, 빠른 스위칭 속도, 간단한 구동 회로, 낮은 구동 전력, 낮은 온 상태 전압, 낮은 스위칭 손실, 넓은 안전 작동 영역, 작은 크기, 높은 전류 밀도, 높은 전류 용량, 높은 내구성 전압, 펄스 전류 충격에 대한 강한 저항 및 2차 항복 없음. IGBT는 Power MOSFET에 비해 스위칭 속도가 느리고 래치 없이 쉬운 단점이 있습니다. IGBT는 내전압이 600V 이상, 전류가 10A 이상, 주파수가 1kHz 이상인 분야에서 주로 사용됩니다.

5.5.2 IGBT는 어떻게 작동합니까?

5.5.2.1 IGBT의 기본 구조

IGBT의 구조는 Power MOSFET의 구조와 매우 유사합니다. IGBT의 게이트(G)는 MOSFET의 게이트(G)에 해당합니다. IGBT의 이미터(E)는 MOSFET의 소스(S)에 해당합니다. IGBT의 컬렉터(C)는 MOSFET의 드레인(D)에 해당합니다. 그러나 IGBT는 기판 영역에 P+ 주입 층위 있어 IGBT가 사이리스터와 같은 P-N-P-N 구조가 됩니다. IGBT는 N+ 버퍼 측을 포함하는지에 따라 PT(Punch-Through) 유형과 NPT(Non-Punch-Through) 유형으로 나눌 수 있습니다. PT형 IGBT는 낮은 스위칭 손실, 낮은 온 상태 손실 및 큰 전류 용량의 장점이 있지만 온도 특성이 NPT 만큼 좋지 않고 병렬연결에 적합하지 않습니다. PT 유형 IGBT의 순방향 항복 전압은 역방향 항복 전압보다 높으므로 DC 회로에 더 적합합니다. NPT 유형 IGBT의 순방향 항복 전압은 역방향 항복 전압과 동일하므로 AC 회로에 더 적합합니다. P-Channel IGBT의 스위칭 속도는 N-Channel IGBT보다 2-3배 느리기 때문에 P-Channel IGBT의 SOA(Safe Operating Area)는 N-Channel IGBT보다 작으며 P의 비용은 -Channel IGBT는 N-Channel IGBT보다 높기 때문에 실제 사용 시 P-Channel IGBT는 드물다. 다음은 주로 PT형 N-Channel IGBT를 소개합니다.

PT형 N-Channel IGBT의 등가 회로도는 기생 향상 N-MOSFET, 기생 JFET, 기생 PNP 트랜지스터 V1(P+ N-P), 및 기생 NPN 트랜지스터 V2(N+ P N-) 및 등가 확장 저항 R2, 그림 51, a. 이 회로에서 V1은 주 출력 채널입니다. V2는 MOSFT의 형성으로 형성됩니다. JFET는 주로 N-드리프트 영역에 의해 형성됩니다. R2는 주로 V2의 P 베이스 영역의 등가 저항에 의해 형성됩니다. 기생 JFET는 주로 N-드리프트 영역의 등가 저항에 의해 형성되는 등가 변조 저항 R1로 더욱 단순화될 수 있습니다. 그런 다음 IGBT의 등가 회로도를 그림 51, b와 같이 단순화할 수 있습니다. IGBT의 4층 반도체 구조(P-N-P-N)는 기생 사이리스터 SCR로 간주할 수 있으며 IGBT의 등가 회로도는 그림 51, c와 같이 더욱 단순화할 수 있습니다. IGBT가 큰 전류 스위칭 능력을 가진 MOSFET으로 간주된다면, P+와 N+ 영역은 파워 다이오드 VD1로 간주될 수 있고, IGBT의 등가 회로도는 그림과 같이 더욱 단순화될 수 있습니다. 그림 51, d. 단순화된 등가 회로도는 IGBT의 작동 원리를 직관적으로 이해하는 데 도움이 됩니다.

5.5.2.2 IGBT의 작동 원리

간단히 말해서 IGBT의 작동 원리는 전압 구동 사이리스터입니다.

순방향 차단 상태: IGBT에 순방향 전압이 적용되고 게이트와 이미터가 단락되면 IGBT는 순방향 차단 상태가 됩니다. 이때, PN 접합 J1, J3는 순방향 바이어스이고, PN 접합 J2는 역방향 바이어스이다. 역 전압은 J2 양쪽의 공핍층이 P 베이스 영역과 N 드리프트 영역으로 확장되도록 합니다.

역 차단 상태: IGBT에 역 전압이 가해지면 PN 접합 J1이 역 바이 어스되고 역 전압은 J1의 공핍층이 다음으로 확장됩니다. N-버퍼 영역. N-버퍼 영역의 너비를 늘리면 IGBT의 역 차단 기능이 향상될 수 있지만 IGBT의 순방향 전압 강하도 증가합니다. IGBT의 역내 전압은 보통 수십 볼트에 불과하므로 IGBT가 역 차단 상태에서 동작하지 않도록 FRED를 IGBT에 약 병렬로 연결한다. 물론 편의를 위해 IGBT와 FRED를 함께 패키징 하여 역전도 IGBT 모듈을 구성합니다.

전도 상태: IGBT에 순방향 전압이 인가되고 게이트에 특정 전압이 인가되면 P 베이스 영역은 N 서브 채널 영역을 형성하여 전자가 N+ 이미터 영역에서 N- 드리프트로 전달되도록 합니다. 지역. 이 전자 흐름은 N 베이스 영역의 전위를 감소시키고 V1에 대한 베이스 전류 IB1를 제공합니다. 이 전자 흐름에 의해 생성된 전압 강하는 약 0.7V 이면 PN 접합 J1이 순방향 바이 어스되고 IGBT가 켜지기 시작합니다. IGBT의 N-드리프트 영역은 매우 넓고 도핑 농도가 낮기 때문에 N-드리프트 영역은 전도도가 매우 낮습니다. IGBT가 고전류에서 작동할 때 컨덕턴스 변조 효과로 인해 N-염기 영역의 캐리어 농도가 증가하고 전도도가 증가하여 컬렉터와 이미 터 사이의 포화 전압과 IGBT의 전체 온 상태 전력 소비가 감소합니다. 전자전류 IN과 정공전류 IP가 있을 때 IGBT는 완전히 온 상태가 된다. IGBT가 켜진 상태일 때 래치업 효과를 피하기 위해 컬렉터 전류를 제한해야 합니다.

차단 상태: 게이트 전압 UGE가 임계 전압 UT보다 낮거나 게이트에 역 바이어스 전압이 인가되면 N 서브 채널이 사라집니다. , IGBT의 베이스 전류가 차단되고 IN 및 IP가 사라지고 IGBT는 차단 상태로 들어갑니다. 그러나 소수 캐리어 효과로 인해 IGBT 출력 전류가 즉시 0으로 감소하지는 않지만 UCE, IC 및 TC와 관련된 특성을 갖는 BJT와 같은 테일 전류가 생성됩니다. 소수 캐리어 효과는 IGBT의 스위칭 시간과 스위칭 손실을 증가시킵니다.

* 래치업 효과

일반적으로 R2는 V2가 작동하지 않도록 V2의 베이스와 이미터를 단락 시킵니다. R2를 통해 흐르는 전류가 너무 커서 R2의 순방향 전압 강하는 트리거 전류 IB2를 제공하기에 충분할 때 V2의 경우 V1 및 V2는 등가 사이리스터 SCR(P+ N-P N+)을 형성합니다. 등가 사이리스터 내부의 포지티브 피드백 메커니즘으로 인해 V1 및 V2는 깊은 포화 상태에 들어가므로 IGBT의 채널은 게이트 전압과 IGBT는 매우 큰 역전압이 인가되는 경우에만 차단될 수 있습니다. 이러한 현상을 래치업 효과라고 하며 정적 래치 법과 동적 래치 법으로 나눌 수 있습니다. 정적 래치 업은 등가 사이리스터가 완전히 켜졌을 때 과도한 컬렉터 전류 IC에 의해 발생합니다. 동적 래치 업은 IGBT의 스위칭 과정에서 과도한 di/dt 및 dv/dt로 인한 큰 변위 전류로 인해 발생합니다. 동적 래치 업을 일으키는 컬렉터 전류는 정적 래치 업보다 작습니다. 래치업 효과는 V1와 V2가 Darlington 구조를 형성하게 하여 IC와 IGBT의 소비전력이 크게 증가하게 되며, IGBT가 손상됩니다. 래치업 효과를 피하기 위해 일반적으로 다음과 같은 조치를 취합니다.

● 내부 구조를 변경하고 V2가 켜지는 것을 방지하기 위해 IGBT를 도핑 하여 R2를 줄입니다.

● V1의 전류 이득 α(일반적으로 0.5 미만)를 줄이기 위해 N-버퍼 레이어의 폭과 도핑을 최적화하여 V2의 작업을 억제합니다.

5.5.3 IGBT의 주요 매개변수

IGBT의 대부분의 매개변수는 MOSFET의 주요 매개변수와 동일합니다.

1- 래핑 전류 IL

래핑 전류 IL은 IGBT의 래치업 효과를 일으키는 컬렉터 전류 값을 나타냅니다. 래핑 전류 IL은 일반적으로 ICM(직류)의 5배 이상입니다. IL 래핑 전류는 IGBT의 현재 용량을 제한하는 주요 원인 중 하나였습니다. 그러나 기술의 발달에 따라 IGBT를 설계하고 사용할 때 정적 래치 업을 고려할 필요가 없지만 여전히 동적 래치 업을 방지하는 것은 필요합니다.

5.5.4 IGBT의 기본 특성

5.5.4.1 IGBT의 정적 특성

1- 입력 특성

IGBT의 정적 입력 특성 곡선은 MOSFET의 정적 입력 특성 곡선과 유사합니다.

2- 출력 특성

IGBT의 정적 출력 특성은 순방향 차단 영역, 활성 영역, 포화 영역 및 역방향 차단 영역으로 나눌 수 있습니다. IGBT는 일반적으로 활성 영역에서 작업할 때 과도한 전력 소모로 인해 IGBT가 소진되는 것을 방지하기 위해 스위칭 상태(즉, 순방향 차단 영역과 포화 영역 사이를 빠르게 앞뒤로 전환)에서만 작동합니다.

전방 차단 영역: BJT의 차단 영역과 유사합니다. UGE < UT, IGBT의 내부 MOS 채널이 꼬이고 컬렉터와 이미터 사이에 누설 전류 ICEO가 있습니다.

활성 영역: BJT의 활성 영역(증폭 영역)과 유사합니다. UGE ≥ UT 및 UCE > UGE - UT, IGBT는 활성 영역에서 작동하며 0.7V 온 상태 전압 강하를 생성합니다. 활성 영역에서 N 베이스 영역으로 흐르는 전자 전류 IN는 베이스 전류 IB1를 제한하는 게이트 전압 UGE에 의해 제어됩니다. V1, 그리고 정공 전류 IP가 제한되므로 컬렉터 전류 IC는 포화 상태( MOSFET의 포화 상태와 유사). 활성 영역에서 IGBT가 부담하는 전압과 전류는 매우 크고 IGBT의 소비 전력도 매우 크므로 IGBT는 가능한 한 빨리 이 영역을 통과해야 합니다.

포화 영역: BJT의 포화 영역과 유사합니다. IGBT의 포화 영역은 옴 영역 또는 가변 저항 영역이라고도 합니다. UGE ≥ UT 및 UCE ≤ UGE - U<sub&gT;T, 컬렉터 전류 IC는 더 이상 게이트 전압 UGE에 의해 제어되지 않고 외부 회로에 의해 결정됩니다.

역 차단 영역: 파워 다이오드의 역 차단 상태와 유사합니다.

* MOSFET 포화 영역과 IGBT 포화 영역의 차이점

IGBT가 완전히 턴 온 된 후의 포화 전압 강하는 주로 컨덕턴스 변조에 의존하는 반면 MOSFET의 턴 온 전압 강하는 주로 드레인 전류(저항 특성)에 의존합니다. 따라서 MOSFET의 포화 영역은 전류 포화를 나타내고 IGBT의 포화 영역은 전압 포화를 나타냅니다.

5.4.2 IGBT의 동적 특성

IGBT의 동적 특성은 MOSFET과 BJT의 조합과 유사합니다.

1- 켜기 프로세스

IGBT의 턴 온 프로세스는 MOSFET의 턴 온 프로세스와 유사합니다. 일반적으로 UGS에서 10% UGS1까지 IC에서 10% IC1를 켜기 지연 시간 td(on)라고 합니다. IC가 10% IC1에서 90% IC1까지 상승하는 데 걸리는 시간을 상승 시간 tr. IGBT의 턴 온 시간 ton은 td(on)와 tr의 합이다. 그러나 UCE의 하강 과정은 두 단계로 나뉩니다. tfv1 단계는 등가 MOSFET이 단독으로 작동하는 단계입니다. tfv2 단계는 등가 MOSFET과 등가 BJT가 함께 작동하는 단계입니다.

켜짐 시간의 계산 공식: ton = td(on) + tr

2- 종료 프로세스

IGBT의 턴오프 프로세스는 MOSFET 및 BJT의 턴오프 프로세스와 유사합니다. 일반적으로 UGS가 90%로 떨어지는 데 걸리는 시간 UGS1에서 IC가 90%로 떨어지는 IC1를 끄기 지연 시간 td(off)라고 합니다. IC가 90% IC1에서 10% IC1으로 떨어지는 데 걸리는 시간을 하강 시간 tf. MOSFET의 턴오프 시간 toff는 td(off)와 tf의 합입니다. 그러나 IC의 하강 과정은 두 단계로 나누어집니다. tfi1 단계는 등가 MOSFET이 단독으로 작동하는 단계입니다. tfi2 단계는 등가 MOSFET과 등가 BJT가 함께 작동하는 단계입니다. 테일 타임 tt는 역 회복 전류가 사라지는 데 필요한 시간이다. P+ 컬렉터 영역에 주입된 정공으로 인해 P+ 컬렉터 영역에서 재결합되어 잔류 전류가 감소하고 tf가 단축됩니다.

꺼짐 시간의 계산 공식: toff = td(off) + tf = td(off) + tfi1 + tfi2

5.5.4.3 IGBT의 안전한 작동 영역

FBSOA(포지티브 바이어스 안전 작동 영역): ICM, UCEM 및 PCM에 의해 결정됩니다.

역 바이 어스된 안전 작동 영역(RBSOA): ICM, UCEM 및 dUCE/dt에 의해 결정됩니다.

5.5.5 IGBT의 직렬 및 병렬연결

MOSFET과 유사하게 IGBT는 직렬연결에 적합하지 않습니다.

IGBT의 온 저항 RON의 온도 특성은 컬렉터 전류 IC의 영향을 받습니다. IC ≤ 1/3 ICM일 때 IGBT의 온 저항 RON은 음의 온도 계수를 가지므로 적합하지 않습니다. 병렬연결. IC > 1/3 ICM, IGBT의 온 저항 RON은 양의 온도 계수를 나타내므로 MOSFET과 마찬가지로 병렬연결에 적합합니다. 전류가 작을 때 IGBT에 대한 불균일한 전류의 영향은 상대적으로 작기 때문에 전체 IGBT는 여전히 병렬연결에 매우 적합합니다.

5.6 기타 완전 제어 장치

복합 구조를 통해 MCT, SIT, SITH, IGCT 등과 같은 여러 장치의 장점을 통합한 완전 제어 장치를 제조할 수 있습니다.

1-MOS 제어 사이리스터

MOS 제어 사이리스터(MCT)는 MOSFET과 사이리스터의 장점을 결합하여 매우 높은 di/dt 및 dv/dt 허용 오차, 빠른 스위칭 속도, 낮은 온 상태 전압, 작은 스위칭 손실, 높은 전압 용량 및 높은 전류 용량. GTO와 마찬가지로 MCT는 수만 개의 MCT 단위로 구성되며 각 단위는 PNP 사이리스터와 MOSFET으로 구성됩니다. MOSFET은 PNP 사이리스터의 작동 상태를 제어합니다. 그러나 MCT의 개념은 IGBT와 유사하지만 전압과 전류 용량이 기대치에서 멀고 가격이 IGBT보다 높아 시장에 내놓을 수 없다.

2- 정전기 유도 트랜지스터

SIT(Static Induction Transistor)는 전도 과정에 다수의 캐리어가 참여하는 일종의 접합 전계 효과 트랜지스터입니다. SIT의 동작 주파수는 Power MOSFET과 같거나 더 높으며 전력 용량은 MOSFET보다 크므로 고주파 및 고 전력 애플리케이션에 적합합니다. SIT는 NO(Normally Open) 스위치입니다. 신호가 적용되지 않으면 SIT가 켜집니다. 음의 바이어스가 적용되면 SIT가 꺼집니다. 실제 적용에서 상시 개방 스위치는 상시 폐쇄 스위치만큼 안전하지 않습니다. 또한 SIT의 온 상태 저항이 크고 온 상태 손실도 크기 때문에 SIT는 Power MOSFET처럼 널리 사용될 수 없다. SIT는 주로 레이더 통신 장비, 초음파 전력 증폭, 펄스 전력 증폭 및 고주파 유도 가열 분야에서 사용됩니다.

3- 정전기 유도 사이리스터

SITH(정적 유도 사이리스터)는 밤이 폴라 필드 제어 사이리스터(FCT)입니다. SITH의 많은 특성은 GTO와 유사합니다. SITH는 컨덕턴스 변조 효과, 낮은 온 상태 전압 및 큰 전류 용량의 장점이 있습니다. SITH의 스위칭 속도는 GTO보다 훨씬 빠르며 현재 턴 오프 이득은 GTO보다 작습니다. SITH에는 일반적으로 열려 있는 유형과 일반적으로 닫히는 유형이 있습니다.

4- 통합 게이트 정류 사이리스터

통합 게이트 정류 사이리스터(IGCT 또는 GCT)는 IGBT와 GTO의 장점을 결합합니다. 전력 용량은 GTO와 동일하며 스위칭 속도는 GTO의 10배입니다. IGCT는 복잡한 버퍼 회로가 필요하지 않지만 구동력은 여전히 큽니다. IGCT와 IGBT는 모두 고 전력 분야에서 GTO를 대체할 수 있습니다.

§6. 전력 전자 장치를 선택하는 방법

6.1 공통 전력 전자 장치

1) 제어할 수 없는 장치

● 범용 다이오드(GPD)

장점: 높은 역전압 피크 전압, 낮은 순방향 전압 강하, 강력한 정류 능력.

단점: 역 회복 시간이 길고 작동 빈도가 낮습니다.

● 고속 복구 다이오드(FRD)

장점: 짧은 역 회복 시간, 높은 작동 주파수, 낮은 순방향 전압 강하 및 높은 피크 역 전압.

단점: 약한 정류 능력.

● 쇼트키 배리어 다이오드(SBD)

장점: 극도로 짧은 역 회복 시간, 극도로 높은 작동 주파수, 극도로 낮은 순방향 전압 강하.

단점: 정상 정류 능력, 낮은 피크 역전압, 높은 온도 감도 및 큰 누설 전류.

2) 반 제어 장치

● 고속 스위칭 사이리스터(FST)

장점: 짧은 스위칭 시간, 높은 작동 주파수, 높은 dv/dt 및 di/dt 허용 오차.

단점: 낮은 정격 전압 및 낮은 정격 전류.

● 3극관 AC 스위치(TRIAC)

장점: 역방향 특성은 순방향 특성과 동일하며 AC 회로에서 작동할 수 있습니다.

단점: 역 차단 기능이 없습니다.

● 역전도 사이리스터(RCT)

장점: 낮은 온 상태 전압, 짧은 턴 오프 시간, FST보다 훨씬 높은 작동 주파수, 높은 정격 접합 온도, 높은 전압 용량, 회로 설계를 단순화할 수 있는 통합 전원 다이오드.

● LTT(Light Triggered Thyristor)

장점: 광학 트리가 링은 제어 회로와 주 회로 사이의 우수한 절연, 강력한 전자기 간섭 방지 기능, 매우 큰 전류 용량 및 매우 큰 전압 용량을 보장할 수 있습니다. 현재 가장 높은 전력 용량을 가진 전력 전자 장치입니다.

단점: 일반적으로 작동 빈도가 높지 않습니다.

3) 완전 제어 장치

● 게이트 턴 오프 사이리스터(GTO)

장점: 대 전압 용량, 대전류 용량, 고 전력 응용 분야에 적합, 전도도 변조 효과, 낮은 전류 차단 이득 및 우수한 열 안정성.

단점: 낮은 스위칭 속도, 큰 음의 게이트 펄스 턴 오프 전류, 큰 구동 전력 및 복잡한 구동 회로.

비고: GTO는 고 전력(메가와트 수준), 고전압 및 낮은 스위칭 주파수를 위한 첫 번째 선택입니다.

● 거대 트랜지스터(GTR)

장점: 큰 전압 용량, 큰 전류 용량, 중간 전력 애플리케이션에 적합, 우수한 스위칭 특성, 낮은 포화 전압 강하.

단점: 낮은 스위칭 속도, 전류 구동, 큰 구동 전력, 복잡한 구동 회로, 2차 고장, IGBT보다 높은 가격.

비고: IGBT의 용량이 증가함에 따라 GTR은 점차 역사의 무대에서 물러날 것입니다.

● 파워 MOSFET

장점: 빠른 스위칭 속도, 높은 입력 임피던스, 우수한 열 안정성, 낮은 구동 전력, 간단한 구동 회로, 높은 작동 주파수 및 2차 고장 없음.

단점: 작은 전류 용량, 낮은 내전압, 일반적으로 전력이 10kW를 초과하지 않는 전력 전자 장치에만 적합합니다.

비고: 전력 MOSFET은 중소 전력, 저전압 및 높은 스위칭 주파수를 위한 첫 번째 선택입니다.

● 절연 게이트 양극성 트랜지스터(IGBT)

장점: 높은 스위칭 속도, 낮은 스위칭 손실, 펄스 전류 영향을 견딜 수 있는 능력, 낮은 온 상태 전압 강하, 높은 입력 임피던스, 전압 구동, 낮은 구동 전력, 2차 항복 없음.

단점: 스위칭 속도가 Power MOSFET보다 느리고 전압 및 전류 용량이 GTO 만큼 좋지 않습니다.

비고: IGBT는 중간 전력, 고전압 및 낮은 스위칭 주파수를 위한 첫 번째 선택입니다.

● MOS 제어 사이리스터(MCT)

장점: 매우 높은 di/dt 및 dv/dt, 매우 빠른 스위칭 속도, 낮은 전도 전압 강하, 작은 스위칭 손실, 높은 전압 용량 및 높은 전류 용량을 견딜 수 있습니다.

단점: 전압 용량과 전류 용량은 IGBT보다 작지만 비용은 IGBT보다 높습니다.

● 정전기 유도 트랜지스터(SIT)

장점: 작동 주파수는 Power MOSFET보다 크고 전력 용량은 Power MOSFET보다 큽니다.

단점: 일반적으로 열려 있고, 온 상태 저항이 크며, 온 상태 손실이 큽니다.

● 정전기 유도 사이리스터(SITH)

장점: 컨덕턴스 변조 효과, 낮은 온 상태 전압 강하, 큰 전류 용량, 스위칭 속도는 GTO보다 빠르고 전류 턴 오프 이득은 GTO보다 작습니다.

단점: 대부분 정상적으로 열립니다.

● 집적 게이트 정류 사이리스터(IGCT)

장점: 전력 용량은 GTO와 동일하고 스위칭 속도는 GTO의 10배이며 복잡한 버퍼 회로가 필요하지 않습니다.

단점: 높은 구동력.

6.2 전원 모듈

이전 장에서 점점 더 많은 전력 전자 장치가 모듈화되기 시작했다고 언급했습니다. 모듈화란 장치의 제조 비용을 줄이고 장치의 부피를 줄이기 위해 여러 장치를 모듈에 패키징 하는 것을 말합니다. 동시에 모듈화로 인해 회로의 리드가 줄어들기 때문에 회로 설계가 단순화되고 회로 인덕턴스도 크게 감소하여 보호 회로 및 버퍼 회로에 대한 수요를 줄이고 회로 설계를 더욱 단순화하여 회로를 만들 수 있습니다. 더 듬직해요.

일반적인 전원 모듈에는 솔리드스테이트 사이리스터 모듈, 솔리드스테이트 전원 다이오드 정류기 모듈, 솔리드스테이트 완전 제어 브리지 정류기 모듈 및 솔리드스테이트 하프 제어 브리지 정류기 모듈이 포함됩니다. 제품 페이지를 클릭하여 전원 모듈에 대한 자세한 정보를 얻을 수 있습니다.

§7. 전력전자기기 사용법

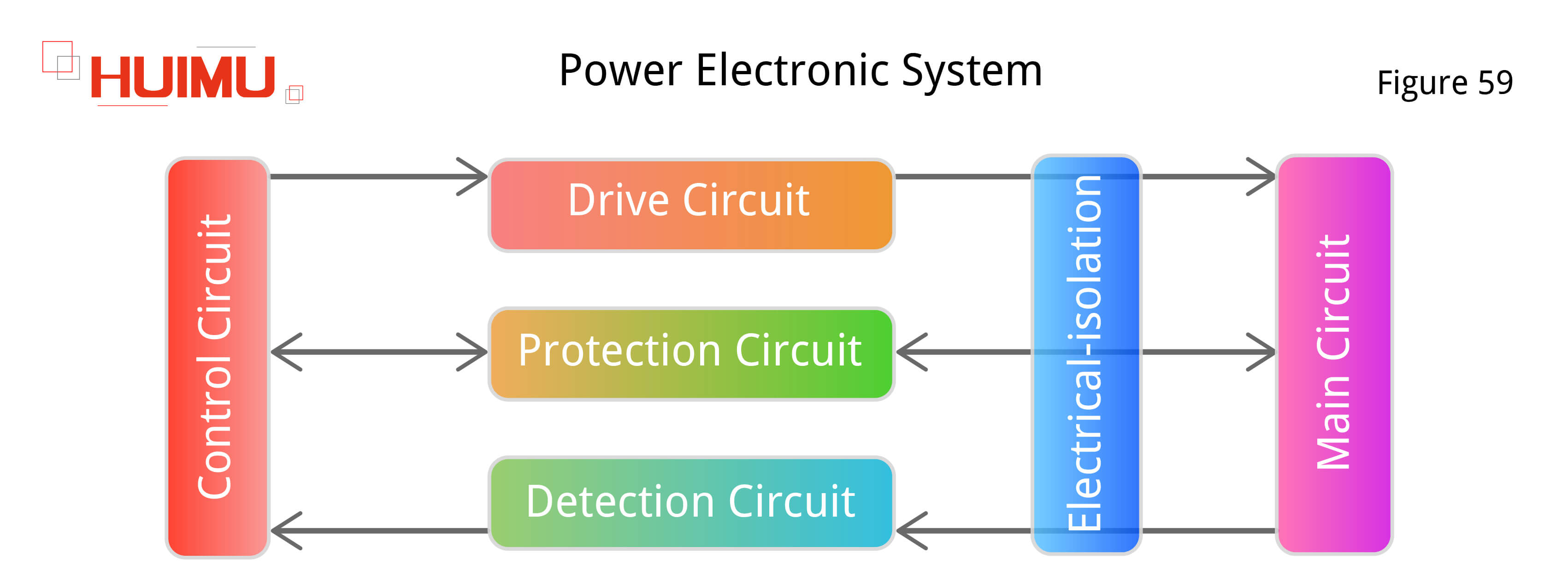

7.1 전력전자 시스템 소개

전력전자기기는 직접 사용할 수 없으며, 전력전자 시스템(PES)을 먼저 구축해야 한다. 전력전자 시스템은 주 회로, 제어회로, 구동회로, 검출 회로, 보호회로로 구성된다.

주 회로 : 전기에너지의 변화나 제어를 실현하는 데 사용한다. 전력 전자 장치는 주 회로의 핵심 부품입니다.

제어 회로: 구동 회로에 제어 신호를 제공하는 데 사용됩니다.

구동 회로: 제어 회로의 제어 신호를 주 회로의 게이트 신호로 변환하는 데 사용됩니다.

검출 회로: 주 회로의 동작 상태를 검출하여 제어회로에 피드백하는 데 사용한다.

보호 회로: 전체 시스템의 안정적인 작동을 보장하기 위해 제어 회로와 주 회로를 보호하는 데 사용됩니다.

전기적 절연 : 제어회로(작은 전류)를 주 회로(대전류)로부터 절연시키기 위해 사용한다.

가장 일반적인 전력 전자 장치로서 무접점 계전기의 내부 구조는 기본 전력 전자 시스템입니다(제로 크로싱 AC 무접점 계전기의 작동 원리).

7.2 전력 전자 장치를 구동하는 방법

구동회로는 주 회로와 제어회로 사이의 인터페이스이며, 제어회로의 제어신호를 주 회로의 턴 온 신호 또는 턴 오프 신호로 변환하는 데 사용된다. 반 제어 장치의 경우 드라이브 회로는 켜기 신호만 제공하면 됩니다. 완전히 제어되는 장치의 경우 구동 회로는 켜기 신호와 끄기 신호를 제공해야 합니다. 구동 회로를 설계할 때 전력 전자 장치가 이상적인 상태에서 작동하려면 많은 요소를 고려해야 합니다. 좋은 구동 회로는 전력 전자 장치의 스위칭 시간 및 스위칭 전력 소비를 효과적으로 감소시킬 수 있으며 동시에 전력 전자 장치의 작업 효율성, 안전성 및 신뢰성을 보장할 수 있습니다.

구동 신호의 종류에 따라 구동 회로는 전류 구동 회로와 전압 구동 회로로 나눌 수 있습니다. 전류 구동 회로는 전류 구동 신호 및 전류 구동 장치에 대한 임계 전압을 제공할 수 있으며; 전압 구동 회로는 전압 구동 장치에 전압 구동 신호를 제공할 수 있습니다. 전압 구동 회로는 전류 구동 회로보다 설계 및 제조가 더 쉽기 때문에 전압 구동 장치가 더 대중적입니다. 구동 회로는 또한 개별 구동 회로와 통합 구동 회로로 나눌 수 있다. 개별 구동 회로는 다양한 전력 전자 장치에 대해 별도로 설계되어야 하며 매개변수 일치 및 전자기 호환성과 같은 문제도 고려해야 합니다. 따라서 전력전자소자의 최상의 성능을 얻기 위해서는 일반적으로 소자 제조사에서 특별히 개발한 통합 구동회로 가 선호된다.

제어 회로는 일반적으로 작동 전력이 매우 낮은 정보 전자 장치로 구성되고 주 회로의 전력이 매우 크기 때문에 구동 회로는 신호를 방지하기 위해 제어 회로와 주 회로 사이에 전기적 절연을 제공해야 합니다. 주 회로에서 제어회로가 손상되지 않도록 하십시오. 절연 방법은 일반적으로 광 절연과 변압기 절연(자기 절연)으로 나눌 수 있습니다.

1- 광학 절연

광 절연은 빛을 통해 제어 신호를 주 회로로 전송하는 것을 말합니다. 일반적으로 광커플러(optocoupler, OPT)는 사광 절연을 위해 사용되며, 광 케플러의 발광다이오드(LED)는 광신호를 통해 광 트랜지스터를 제어한다. 포토커플러의 입력 전류 ID는 일반 트랜지스터의 베이스 전류와 동일하고 출력 전류 IC는 일반 트랜지스터의 컬렉터 전류와 동일합니다. 광 케플러의 입력 및 출력 특성은 BJT와 유사합니다. 일반 광 케플러의 전류 이득 ID/IC는 일반적으로 1보다 작습니다. 높은 전송 비율 유형 광 케플러는 전류 이득을 증가시키기 위해 달링턴 구조를 사용하지만 저항 광 케플러의 전압은 제한됩니다(일반적으로 2000V 이내). 광 트리거 사이리스터는 광섬유를 통해 제어 신호를 전송하므로 추가적인 광 절연 조치를 추가할 필요가 없습니다. 동시에 라이트 트리거 사이리스터는 반 제어 장치이므로 끄는 방법을 고려할 필요가 없습니다.

2- 변압기 절연

변압기 절연은 펄스 변압기의 철심을 통해 1 차 권선과 2 차 권선을 절연하고 철심의 자기 포화 특성을 사용하여 제어 신호를 입력 회로에서 출력 회로로 전송하는 것을 말합니다. 변압기의 비선형 왜곡 특성으로 인해 펄스 변압기는 일반적으로 고주파 신호에 적합하므로 발열 및 손실도 고려해야 합니다. 펄스 변압기는 일반적으로 코어의 초기 투자율에서 작동하기 때문에 펄스 변압기의 부피는 다른 변압기보다 훨씬 큽니다.

7.2.1 반 제어 장치의 구동 회로

1- 켜기 요구 사항

● 일정한 펄스 폭(펄스 유지 시간)을 확보하여 사이리스터의 내부 포지티브 피드백이 확립되어 사이리스터의 안정적인 전도를 보장할 수 있도록 합니다.

● 충분한 구동 전류를 제공하기 위해 일정한 펄스 플랫 상단 진폭을 확인하고 동시에 사이리스터의 정상적인 작동을 방해하는 버의 출현을 피하십시오.